根據(jù)v1版本使用記錄和市場(chǎng)評(píng)測(cè)進(jìn)一步完善,以應(yīng)用于更多的實(shí)際產(chǎn)品

邊緣AI領(lǐng)域的領(lǐng)先標(biāo)桿企業(yè)LeapMind有限公司今日公布了其正在開發(fā)和授權(quán)的超低功耗AI推理加速器IP “Efficiera” v2版本(以下簡(jiǎn)稱“v2”)。LeapMind于2021年9月發(fā)布了Efficiera v2的測(cè)試版,并收到了許多公司的測(cè)試及反饋,包括SoC供應(yīng)商和終端用戶產(chǎn)品設(shè)計(jì)師。Efficiera v2預(yù)計(jì)2021年12月開始發(fā)售,如有意向獲取,請(qǐng)通過(guò)此郵箱垂詢:business@leapmind.io。

LeapMind首席執(zhí)行官Soichi Matsuda表示:“去年,我們正式推出了v1的商用版本,許多公司對(duì)Efficiera進(jìn)行了評(píng)測(cè)。截至2021年9月底,我們共與8家日本國(guó)內(nèi)公司簽署了授權(quán)協(xié)議。‘向世界傳播采用機(jī)器學(xué)習(xí)的新設(shè)備’是我們根據(jù)企業(yè)理念所設(shè)定的座右銘,而我們正通過(guò)提供v1來(lái)穩(wěn)步推進(jìn)這一理念的落地。在未來(lái),我們將進(jìn)一步通過(guò)技術(shù)創(chuàng)新和產(chǎn)品陣容擴(kuò)展,繼續(xù)努力實(shí)現(xiàn)人工智能的普及。”

Efficiera v2根據(jù)v1的使用記錄和市場(chǎng)評(píng)測(cè),擴(kuò)大了應(yīng)用范圍,在保持最小配置的電路規(guī)模基礎(chǔ)上,可覆蓋更廣泛的性能范圍,并應(yīng)用于更多的實(shí)際產(chǎn)品。產(chǎn)品由此得到了進(jìn)一步的完善。

Efficiera v2概念

LeapMind董事兼首席技術(shù)官Hiroyuki Tokunaga博士表示:“自去年發(fā)布v1以來(lái),我們強(qiáng)化了設(shè)計(jì)/驗(yàn)證方法和開發(fā)流程,旨在‘開發(fā)世界上最節(jié)能的DNN加速器’。我們一直在開發(fā)v2,以使產(chǎn)品能夠適用于專用集成電路(ASIC)和專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)。我們還在開發(fā)一個(gè)深度學(xué)習(xí)方面的推理學(xué)習(xí)模型,以便將超小量化技術(shù)的優(yōu)勢(shì)最大化。LeapMind的最大優(yōu)勢(shì)就在于我們可以提供一種技術(shù)來(lái)實(shí)現(xiàn)雙管齊下。”

Efficiera v2的主要規(guī)格與特性

A.在保持最小電路規(guī)模的同時(shí),覆蓋更廣泛的性能范圍,從而擴(kuò)大應(yīng)用范圍。

硬件特性

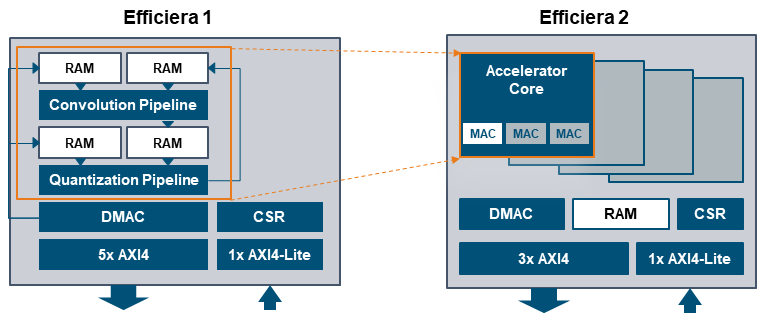

● 通過(guò)多路復(fù)用MAC陣列+多核,性能可擴(kuò)展至48倍

V2允許你將卷積管道中的MAC陣列數(shù)量增加到v1的3倍(可選擇x1、x4),并通過(guò)提供多達(dá)4個(gè)內(nèi)核的選擇,進(jìn)一步擴(kuò)大性能的可擴(kuò)展性。

● 除卷積和量化外,還可實(shí)現(xiàn)硬件執(zhí)行跳過(guò)連接和像素嵌入

1. 跳過(guò)連接是多層卷積神經(jīng)網(wǎng)絡(luò)(CNN)中常見的一種操作。(v1中由CPU執(zhí)行)

2. 像素嵌入是一種對(duì)輸入數(shù)據(jù)進(jìn)行量化的方法

● 資源使用方面,配置與Efficiera 1相同

1. 有些應(yīng)用只因AI功能可在規(guī)模有限的FPGA器件上實(shí)現(xiàn)就能創(chuàng)造價(jià)值。

2. LeapMind分析了一個(gè)實(shí)用型深度學(xué)習(xí)模型的執(zhí)行時(shí)間,并仔細(xì)選擇了額外的硬件功能。

集成到SoC中

● AMBA AXI接口

● AMBA AXI interface

AMBA AXI繼續(xù)被用作與外部的接口,并且當(dāng)接口被視為一個(gè)黑盒子時(shí)與以前一樣,易于從當(dāng)前設(shè)計(jì)中遷移。

● 單時(shí)鐘域

FPGA中的目標(biāo)頻率

● FPGA的運(yùn)行頻率與先前相同,雖然取決于具體設(shè)備,但預(yù)計(jì)約為150到250MHz。

1. 256 GOP/s @ 125MHz (單核)

2. 高達(dá)12 TOP/s @ 250MHz (雙核)

● 以加密RTL的形式提供

B. 通過(guò)改進(jìn)設(shè)計(jì)/驗(yàn)證方法并審查開發(fā)流程,我們確保質(zhì)量不僅適用于FPGA,也適用于ASIC/ASSP。

C. 開始提供一個(gè)模型開發(fā)環(huán)境(NDK),使用戶能夠?yàn)镋fficiera開發(fā)深度學(xué)習(xí)模型。目前為止只有LeapMind實(shí)現(xiàn)了這項(xiàng)工作。

● 為Efficiera創(chuàng)建超小型量化深度學(xué)習(xí)模型所需的代碼和信息包

● GPU深度學(xué)習(xí)模型的開發(fā)者可立即上手使用

● 支持PyTorch和TensorFlow 2的深度學(xué)習(xí)框架

● 學(xué)習(xí)環(huán)境為一個(gè)配備GPU的Linux服務(wù)器

● 推理環(huán)境為一個(gè)配備Efficiera的設(shè)備

● 來(lái)自LeapMind的技術(shù)支持