片上系統(SoC)平臺是異質性的實體。它們通常包含至少一個處理器部件(譬如微處理器或DSP),以及外圍設備、隨機邏輯、嵌入式存儲器、通訊基礎結構和傳感器、傳動裝置之類的外部接口元件。這些變化多樣的設計平臺正在將設計焦點和折衷分析轉移至通訊層面。

由 于SoC內的功能單元常常是通過若干標準及基于數據總線的專有協議來實現通信,所以理解模塊間通訊已經成為驗證的一個關鍵。設計活動向通訊基礎架構設計的 轉移,也促進了對混合級建模以及調試技術的使用。這些技術使設計工程師能夠完全應對從電阻晶體管邏輯電路(RTL)到更高事務處理級的轉移,而且無需中斷 使用目前的功能驗證方法。

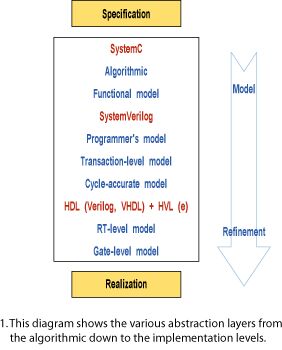

有鑒于現今協議的復雜性,要詳盡理解信號級上的同步互動是艱難而又費時的。此外,由于不同的團隊和個人都將設計視為從規格到實現的提煉過程,所以各個設計團隊之間以及團隊內部都需要找到一個通用參考框架(frame)。

有代表性的參考標準必須足夠靈活以便適合于多個應用領域。它也必須經得起抽象和提煉,以便適用于由上而下設計或由下而上的配置。事務處理級建模(TLM)被用作所需的中間建模抽象級,成為連接頂層和底層的橋梁。

事務處理級建模的概念

目前的SoC設計流程是一個混合過程,包括由上而下的從規格制定到實現、從下而上的設計模塊集成,以及對來自外部供應商或內部重用模塊的知識產權的驗證。事 務處理可以作為連接不同設計建模層間間隙的一個最終優化規范。這包括用高級語言實現的無時序(untimed)純功能性建模、通過架構估計得到大致時序的 功能級,一直到實現級、循環精確的RTL。

除此之外,事務處理級建模也作為系統工程師和專用模塊開發者之間的一個通用描述性媒介而發揮著 作用,該媒介超越了不同的適用于具體設計或驗證活動的語言的界限。于是,事務處理就變成實施構架開發和折衷分析的一種形式。它是一種通過分析系統功能有效 性和性能度量(譬如整體吞吐量、模塊與存儲器交互延遲等)來自動進行設計理解和調試過程的手段。

|

圖1顯示的是從算法級到實現級的各個抽象級,通常包括SystemC(IEEE P1666)、SystemVerilog(IEEE P1800)和e(IEEE P1647)在內的幾種功能建模與驗證語言(及標準)被用于設計。另外,先進的方法實踐,例如從OpenVera的“參考驗證法指南”以及e的“e再使用法推薦”抽取出的方法實踐,為算法、構架以及事務處理級建模提供參考。

事務處理級建模是一個相當普通的應用,它涉及并描述設計的每一個功能線程。事務處理級的焦點是“如何”進行,特別是通訊交互“如何”進行,而不在于功能是 “什么”。事務處理所提供的是執行細節在時間上的抽象與空間上的封裝在――這是最初注重通訊基礎架構而不是功能模塊的思想的體現。做這樣的抽象建模的好處 是驗證效率高。事實上,對事務處理的運用正變得日益廣泛、多種多樣,并成為主流。

在模塊間捕捉同步傳輸的事務處理也注定會成為折衷分析中的重要角色。因此,建模與記錄事務處理對提升基于事務處理的驗證和調試技術非常關鍵,而驗證和調試技術是提高開發效率與設計質量所必須的。

如何進行事務處理級建模

高級語言(也稱為“HLL”,例如SystemC)、其它的硬件驗證語言(也稱為“HVL”,例如OpenVera、e)以及測試向量(testbenchz)與硬件設計語言(例如SystemVerilog)對事務處理都有程度不一的內在支持。SystemC (www.SystemC.org)可為建模語言內置的用戶驅動事務處理的創建提供支持,并可把它們記錄到數據庫中,就如同采用SCV函數庫的sc_trace()寫入數據庫一樣。SCV有許多預先定義的非常有用的類,包括下面三個主要的記錄對象:scv_tr_db: 事務處理數據庫對象,它允許用戶控制記錄。該對象是通用的且獨立于數據庫格式。第三方記錄API供應商可以將底層服務對應到他們自己的數據庫方案中。

scv_tr_stream: 事務處理流建模對象。流是一種抽象通訊方法,包括重疊事務處理在內的事務處理可以發生流中,例如一個帶有讀/寫事務處理的存儲流。因此一個流可以被認為是一個抽象信號,在這個信號中事務處理是可以被信號使用的抽象值,例如一個數據傳送總線的地址或數據流。

scv_tr_generator: 圍繞一個特定的事務處理類別并且允許創建和增加屬性的對象,可以是包括設計信號和信息以及通用有效負載數據在內的任何對象。

下面的代碼段 顯示了如何利用SCV以一種相對比較直接的方式創建事務處理。每一個代碼段前的注釋均指出其后語句的目的。事務處理可以以一種無縫的方式(不需要用戶的直 接干預)被記錄進數據庫中。為了實現這一點,工具供應商可以通過在上述三個類中提供的注冊機制來注冊回叫,從而實現記錄功能。用戶只需要增加一些初始化調 用即可。

// Inside sc_main() or some other context

// SCV startup

scv_startup();

// Initialization

API_vendor_initialization(); // set SCV callbacks here

scv_tr_db db("my_db");

scv_tr_db::set_default_db(&db);

// Define a stream and a generator

scv_tr_stream mem_stream("memory", "transactor");

scv_tr_generator read_gen("read", mem_stream, "mem");

scv_tr_handle tr_handle;

// Modeling code here

// Transaction begin with a tr_data attribute

tr_data.addr= addr_signal;

tr_data.data=data_signal;

tr_handle=write_gen.begin_transaction(tr_data);

// Transaction end

tr_handle.end_transaction();

// Other modeling code here

SCV也有許多其它的類,例如,在不同的事務處理之間建立關系的scv_tr_relation。在確定諸如前續-后繼之類的因果關系、如父-子之類的層次關系以及成分分析集合體時,關系在分析以及調試方面都相當有用。

由于OpenVera(www.open-vera.org)是一種面向對象的建模語言,它可以輕而易舉地容納事務處理級建模的封裝概念。該語言目前不具備與SCV類似的內置事務處理類。但可有可能為了這一目的而創建類,例如下面的極小集:trans_db:用于數據庫;

trans_stream:事務處理流建模對象;

trans_type:創建事務處理以及事務處理的屬性;

trans_handle:便于操控句柄。