摘? 要: 為適應我國高速列車自動控制系統發展的需要,提出采用雙CPU加FPGA的系統設計方案,實現移頻信號發送。在保證移頻信號高相位精度的前提下,實現系統的自動多載頻信號切換和實時故障檢測" title="故障檢測">故障檢測。

關鍵詞: CPU FPGA 移頻 故障檢測

?

移頻信號全稱為移頻鍵控信號(Frequency-Shift Keying),利用高頻信號承載低頻信息,具有抗干擾能力強、傳輸距離遠等優點,是現代鐵路機車行駛中的速度控制信號。它可以準確確定列車的位置,與鐵路機車安全運行有密切的關系。為確保信號接收系統接收到準確、實時有效的信號,要求移頻信號發送系統在發送高精度移頻信號的同時,能夠保證自身系統的故障檢測。

現有的移頻信號發送系統,使用特定頻率晶振和CMOS器件,頻率相位精度低、通用性差,無法實現多載頻信號之間的自動切換,而且自檢能力不高,不能達到實時故障檢測,無法適應我國高速列車發展的需要[1]。因此,設計一種新型的移頻信號發送系統就成為一個迫在眉睫的問題。本文提出采用雙CPU保護下的FPGA系統實現移頻信號發送的設計方案,以FPGA為系統核心,采用固定16MHz頻率晶振,完成CPU時序控制下FPGA的邏輯功能。在保證移頻信號高相位精度的前提下,實現了系統的自動多載頻信號切換和實時故障檢測。

1 FPGA芯片

本文選用的FPGA芯片是Xilinx公司推出的XC4005E-4IPQ100,該類型芯片具有5000最大邏輯門(Max Logic Gate),其中可配置邏輯模塊(CLB)196個,以14×14矩陣結構排列;輸入輸出模塊(IOB)112個。可實現616級觸發器(Flip-Flops),具有并行模式配置能力,存儲器容量為95,008 bits。使用亞微米多層金屬材料加工方法,使系統時鐘速率高達80MHz,而內部執行速度可以達到150MHz[3]。

該類型芯片在原有XC3000系列芯片的基礎上,增加了內部軟啟動結構和時鐘驅動輸入輸出模塊的數目,并且提供了可選擇雙向RAM存儲器。

2 系統設計原理

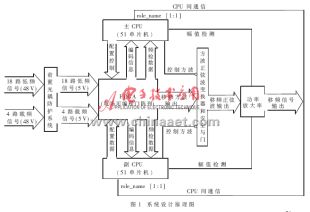

系統設計原理如圖1所示,該系統以雙CPU保護下的FPGA為核心,配以輔助的前置光耦防護和后置安全與門及功率放大器。輸入為國家標準的鐵路用18路低頻信息和4種載頻觸發信號,輸出相應的調制后高精度移頻正弦信號。其中,4種載頻可以由觸發信號直接控制,自動切換。

?

?

FPGA內部邏輯被設計為分頻器、計數器、編碼器、存儲器、觸發器和電子開關" title="電子開關">電子開關等部分。經過邏輯組合,實現低載頻信息編碼、相位連續移頻信號調制" title="信號調制">信號調制和移頻信號檢測" title="信號檢測">信號檢測計數等三個主要功能,并接收CPU的控制信號,完成與CPU間的數據傳輸。

圖1中雙CPU使用W78E58型單片機。主、副CPU各自獨立工作,分別向FPGA發送控制信號,讀取低載頻信息編碼和移頻檢測計數結果,并以此為判據進行移頻信號發送精度檢測。發現誤碼情況,即時關閉安全與門,切斷移頻信號發送通道,保證故障安全。主、副CPU之間,每個程序循環周期通信一次,以確認對方處于正常工作狀態。

3 軟件設計

3.1 移頻信號調制結構設計

圖2示出了FPGA內部實現移頻信號調制的邏輯結構。FPGA芯片選用16MHz時鐘脈沖,在分頻模塊的作用下得到所需要的低頻和載頻信號;運用時鐘同步觸發器和電子開關實現頻率調制過程中的沿同步,從而在保證移頻信號頻率精度的前提下,實現了移頻信號的相位連續調制。

?

?

圖2中K(t)為低頻方波信號,G1(t)、G2(t)為載頻方波信號,CLK為16MHz時鐘脈沖,CS1、CS2為電子開關使能信號。低頻分頻器、載頻分頻器1、載頻分頻器2、時鐘同步觸發器、反相器、電子開關和加法器由FPGA內部邏輯門陣列通過狀態機的方式實現[4]。低頻分頻器和載頻分頻器的分頻數由輸入的低、載頻觸發信號控制,進行自動預置,使信號發送系統適用于多種載頻切換,達到系統的通用性。

FPGA內部邏輯結構使用VHDL語言編寫,圖3示出了移頻信號調制部分的VHDL語言程序流程圖。

?

?

3.2 移頻信號檢測時序設計

移頻信號檢測采用高頻插入的方法。將16MHz標準脈沖插入待測信號中,通過計數器確定待測信號的一個載頻周期Tz,得到其載頻頻率fz:

式中Nz為一個載頻周期內的計數脈沖個數。

為了計算待測移頻信號中的低頻周期,需要存儲大量的載頻周期數Nz。利用CPU的定時器構成一定時間內(0.2s)的Nz數組,尋找移頻信號上下邊頻的切換點,通過計算兩個相鄰切換點之間的載頻周期數,確定低頻周期,得到低頻頻率fd:

式中Nd為兩個相鄰上下邊頻切換點之間的頻率周期數。

在本文中,雙CPU各自獨立完成檢測計數數據的精度判斷和定時器控制,計數器部分在FPGA內部實現,圖4示出了移頻信號檢測原理圖。

?

?

CPU源程序使用C語言編寫,使程序結構化,并易于升級。圖5示出了移頻信號檢測部分的C語言程序流程圖。

?

?

4 性能分析

4.1 實驗結果

在完成調試樣機的基礎上,對新型移頻信號發送系統進行實驗檢測。其中,載頻信號取8種,中心頻率分別為550、650、750和850Hz,頻偏均為55Hz。低頻信息從國家鐵道移頻信號標準中隨機選取8種,分別為7、8、9、9.5、16.5、17.5、18.5和26Hz。

為檢測實際發送的移頻信號,利用HP3563A(Control Systems Analyzer)控制系統分析儀模擬通用移頻信號接收器進行頻譜分析。采樣頻率為2048點/s,加Hanning窗進行FFT變換[2],可得到如圖6所示的信號頻譜圖。其中,兩個波峰處的相應頻率就是FSK信號的上下邊頻,其左右兩側的次高波峰處的相應頻率為上下邊頻的低頻頻偏頻率。考慮到上、下邊頻譜線之間的相互干擾,取能量最高的次高峰為低頻頻偏點,其與相鄰最高波峰之間的頻率差即為對應FSK信號所包含的低頻信息[5]。

?

?

系統自檢部分的驗證,由Micropack公司提供的Easypack/E 8052F在線仿真系統完成。該系統模擬CPU的全部功能,并從FPGA直接讀取移頻檢測數據,數據格式為十六進制。

表1示出了系統實驗結果,其中頻率理論值和測量值單位均為Hz,系統自檢值Nd、Nz1、Nz2均為十六進制數。上、下邊頻自檢計數脈沖為16MHz,低頻自檢計數方波為上邊頻方波。

?

?

4.2 數據分析

對表1中實驗數據進行移頻測量值和自檢值的最大相對誤差" title="相對誤差">相對誤差分析,可以得到本文中新型系統的各方面精度,從而判斷其是否滿足設計要求。

移頻信號測量值的相對誤差可以由下式得到:

式中,fc、fl分別為頻率的測量值和理論值。

結合公式(1)和公式(2),可以得到系統移頻自檢值的相對誤差計算方法:

式中,Ez、Ed分別為載頻自檢相對誤差和低頻自檢相對誤差,fc為對應的低頻或上下邊頻測量值。

由公式(3)、(4)、(5)得到系統頻率測量值和自檢值最大相對誤差如表2所示。

?

?

從表2可以看出,實際移頻信號的發送相對誤差不大于1%,完全滿足鐵道通信信號的精度要求;自檢系統更可以保證實時檢驗發送信號,實現故障安全。

綜上所述,新型移頻信號發送系統應用先進的可編程邏輯芯片(FPGA)和高性能CPU,通過巧妙的邏輯結構設計和時序控制,實現了系統的集成化、通用化,大幅度提高了系統運行速度和可靠性。實驗結果表明,該系統完全能夠滿足高速、高精度、故障安全的鐵道通信信號技術要求,具有很高的應用價值。

?

參考文獻

1 王建國.提高ZP-89型移頻發送電路性能的方法.鐵道通信信號,1999;02:23~24

2 Clifford J P,Wilton S J E.Architecture of clusterbased FPGAS with memory.Proceedings of the Custom Integrated Circuits Conference CICC 2000,2000:131~134

3 柏 溢. FPGA的比較與選型[J].信息工程學院學報,1999;03:61~64

4 Kevin S著.朱明程,孫 普譯.可編程邏輯系統的VHDL設計技術.南京:東南大學出版社,1998?

5 Vitetta G M,Mengali U,Taylor?D.P.Error probability of FSK?incoherent diversity reception?with fast rice fading.International?Journal of Wireless Information?Networks,1999;2:107~118.