旋轉(zhuǎn)變壓器是一種電磁感應(yīng)式傳感器,用來測量旋轉(zhuǎn)物體的轉(zhuǎn)軸角位移和角速度,它由定子和轉(zhuǎn)子組成。其中定子繞組作為變壓器的原邊,接受勵磁電壓,轉(zhuǎn)子繞組作為變壓器的副邊,通過電磁耦合得到感應(yīng)電壓。為了提高測量精度,采用雙通道旋轉(zhuǎn)變壓器。雙通道旋轉(zhuǎn)變壓器采用單相定子激磁、兩相定子感應(yīng)輸出。

AD2S82A和AD2S80A是美國模擬器件公司(Analog Devices Inc)生產(chǎn)的分解器數(shù)字轉(zhuǎn)換器(簡稱RDC)。AD2S8X系列RDC可將轉(zhuǎn)角轉(zhuǎn)換成與轉(zhuǎn)角成比例的數(shù)字量,它實質(zhì)上是一種特殊的模數(shù)轉(zhuǎn)換器。

AD2S82A和AD2S80A都屬于AD2S8X系列中的產(chǎn)品,是一種單片式、分辨率可變RDC。在制造過程中它采用BiMOS工藝,使用雙極性高精度線性電路,因此具有精度高、性能穩(wěn)定及可靠性高等特點。

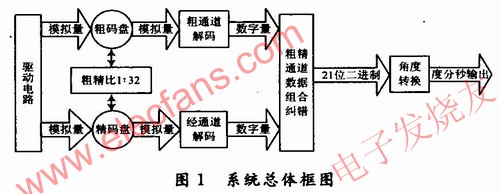

1 總體設(shè)計方案

系統(tǒng)總體框圖如圖1所示,采用集成芯片AD2S82A和AD2S80A,分別作為旋轉(zhuǎn)變壓器粗碼盤和精碼盤輸出信號的解碼器,將旋轉(zhuǎn)變壓器輸出的模擬量轉(zhuǎn)換成與之對應(yīng)的數(shù)字量。然后將它們送入FPGA中進行誤差補償和數(shù)據(jù)組合,再在FPGA中對誤差補償后的二進制角度值,通過分段查表轉(zhuǎn)換為以度分秒顯示的角度值。

2 硬件電路設(shè)計

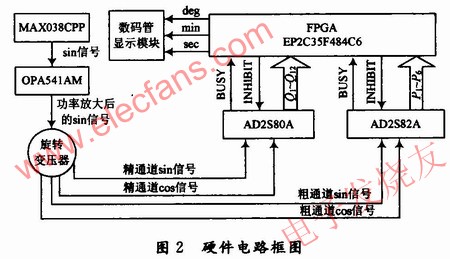

2.1 硬件電路框圖

該硬件電路框圖如圖2所示,F(xiàn)PGA芯片作為系統(tǒng)的設(shè)計核心,對其他電路模塊進行控制,同時在FPGA中實現(xiàn)誤差補償和數(shù)據(jù)組合和角度轉(zhuǎn)換。

2.2 驅(qū)動及A/D轉(zhuǎn)換模塊

驅(qū)動電路主要采用集成芯片MAX038CPP,用其來產(chǎn)生正弦波,由于該正弦波電流很小,不能用其直接驅(qū)動旋轉(zhuǎn)變壓器,還要對其進行功率放大。功率放大電路主要采用集成芯片OPA541AM。

把驅(qū)動電路產(chǎn)生的正弦波作為雙通道旋轉(zhuǎn)變壓器的激勵信號,加到其定子繞組上,于是在其粗通道轉(zhuǎn)子繞組上產(chǎn)生正弦波和余弦波,將它們送入AD2S82A,對其進行解碼。同時,將旋轉(zhuǎn)變壓器精通道轉(zhuǎn)子繞組產(chǎn)生的正弦波和余弦波送入AD2S80A,也進行解碼。

通過AD2S82A和AD2S80A的片選端口,可以選擇它們各自的分辨率10 b,12 b,14 b,16 b,與其對應(yīng)的最高跟蹤速度為1 040 r/s,260 r/s,65 r/s,16 125 r/s。由于它們將旋轉(zhuǎn)變壓器式信號轉(zhuǎn)換成自然二進制代碼,是采用一種比率式跟蹤方法,輸出數(shù)字角只與輸入正余弦信號的比值有關(guān),而與絕對值無關(guān),因此具有較高的噪音抑制能力,可以減小旋轉(zhuǎn)變壓器遠距離傳輸帶來的誤差。這里AD2S82A和AD2S-SOA都選擇12位輸出。

當(dāng)AD2S82A和AD2S80A正處于運算過程當(dāng)中時,會在它們各自的BUSY端口,產(chǎn)生一個繁忙信號。用FPGA對這兩個繁忙信號進行檢測,當(dāng)兩芯片有一塊處在運算過程當(dāng)中時,F(xiàn)PGA發(fā)出一個禁止信號,送入AD2S82A和AD2S80A各自的INHIBIT端口,禁止這時讀取兩芯片的轉(zhuǎn)換數(shù)據(jù)。這樣即能使兩芯片工作同步,又能防止誤讀轉(zhuǎn)換結(jié)果。

2.3 FPGA誤差補償和數(shù)據(jù)組合模塊

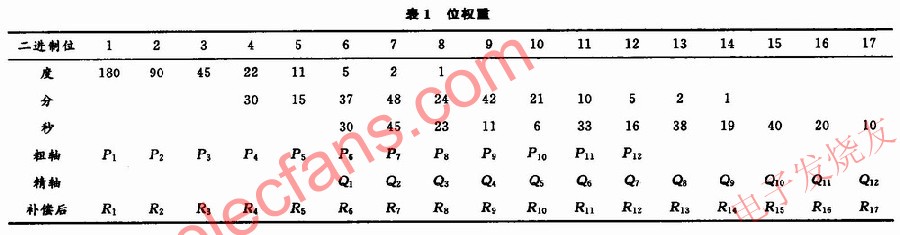

當(dāng)雙通道旋轉(zhuǎn)變壓器粗碼盤和精碼盤的極數(shù)比值為1:32時,旋轉(zhuǎn)變壓器旋轉(zhuǎn)1圈,這時粗軸相當(dāng)于轉(zhuǎn)了1圈,而精軸相當(dāng)于旋轉(zhuǎn)了32圈,也即粗軸旋轉(zhuǎn)1圈相當(dāng)于轉(zhuǎn)過360°,而精軸旋轉(zhuǎn)1圈只轉(zhuǎn)過了11.25°(360°/32)。所以,精軸解碼后的數(shù)字角最高位Q1代表5.625°(11.25°/2),相當(dāng)于粗軸的P6位。解碼后的粗軸和精軸各個位的權(quán)重如表1所示。

由于粗軸的后幾位肯定不如放大32倍之后的精軸的數(shù)字準(zhǔn)確,所以粗精數(shù)字角組合的原則是,粗精軸都輸出12位數(shù)字角,但粗軸只取高5位(P1~P5),而精軸取全12位(Q1~Q12)。

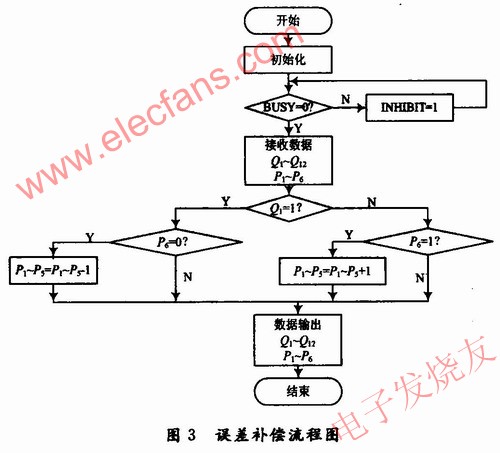

由于旋轉(zhuǎn)變壓器在轉(zhuǎn)動時,粗碼盤和精碼盤之間存在各種各樣的誤差,粗精通道對應(yīng)位可能不同是變化。即存在粗通道數(shù)據(jù)變化后,精通道對應(yīng)位的數(shù)據(jù)還沒有變化,同樣也存在精通道數(shù)據(jù)變化,而粗通道對應(yīng)位的數(shù)據(jù)還沒有變化,因此還要對解碼后的數(shù)據(jù)進行誤差補償。

通過表1可以看出,粗通道和精通道對應(yīng)的位只有P6和Q1,它們都代表5°37’30"。當(dāng)P6和Q1變化不同步時,就要進行誤差補償。采用VHDL語言編寫誤差補償模塊,在FPGA中實現(xiàn)誤差補償,其程序流程圖如圖3所示。

2.4 角度值轉(zhuǎn)換模塊

誤差補償后的角度值,是以二進制顯示的角度,即如表1所示的R1~R17,不同的位代表的角度值不同。為了方便顯示和后續(xù)電路運算,還要對二進制角度值進行轉(zhuǎn)換,將其轉(zhuǎn)換為以度分秒顯示的角度值。直接按各個位的權(quán)重進行轉(zhuǎn)換,涉及到多次乘法和除法運算,影響整個電路的速度。通過查表可以避開免乘法和除法運算,但是直接查表需要很大的ROM空間,這里采用分段查表法,把誤差補償后的數(shù)據(jù)分成整度數(shù)的位R1~R3和帶分秒的位R4~R17,其中R4~R17按度分秒分別進行查表,再將查到的整度數(shù)和R1~R3查到的整度數(shù)做加法運算。這樣可以將ROM空間減小到原來的大約1/8。

3 仿真驗證

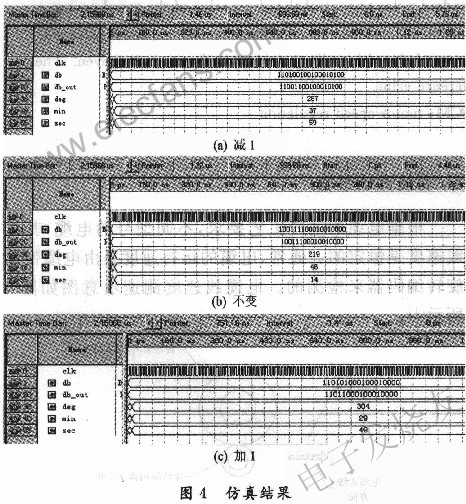

現(xiàn)將誤差補償、數(shù)據(jù)組合、角度轉(zhuǎn)換3個模塊進行仿真。仿真是基于Altera公司的EP2C35F484C6型FGPA,仿真中建立了3種情況的測試平臺,仿真結(jié)果如圖4所示。

仿真的時鐘周期為10 nS,dbl~dbl8為FPGA的輸入信號,其中dbl為最高位。db的高6位dbl~db6為AD2S82A的輸出(P1~P6),db的其他位db7~dbl8為AD2S80A的輸出(Ql~Q12),db_outl~db_out17為誤差補償后的數(shù)據(jù),再用db_outl~db_outl7去分段查表。圖4中deg為度數(shù)輸出,min為分?jǐn)?shù)輸出,sec為秒數(shù)輸出。

從仿真結(jié)果可以看出,當(dāng)db6(P5)和db7(Q1)不同時,就要進行誤差補償。誤差補償后的數(shù)據(jù)再通過分段查表,就可以得到正確的以度分秒顯示的角度值。

4 結(jié)語

提出并建立了一種基于FPGA的雙通道旋轉(zhuǎn)變壓器測角系統(tǒng)。該方案的主要特點是充分利用了FPGA豐富的硬件資源,將復(fù)雜的數(shù)學(xué)運算和控制運算用硬件來實現(xiàn),大大提高了轉(zhuǎn)換的速率和整個系統(tǒng)的穩(wěn)定性。該方案也可以輕松地移植到更多極對數(shù)的旋轉(zhuǎn)變壓器或感應(yīng)同步器上,可進一步提高轉(zhuǎn)換的精度。