摘 要: 介紹了一種帶有48字節(jié)RAM的日歷時(shí)鐘" title="日歷時(shí)鐘">日歷時(shí)鐘芯片的設(shè)計(jì),該芯片具有振蕩、分頻、可編程的計(jì)時(shí)計(jì)數(shù)、定時(shí)鬧響和中斷輸出等功能。該芯片基于Verilog HDL描述,采用模塊化設(shè)計(jì),可擴(kuò)展性好;并利用Synopsys公司的VCS和DC工具分別對(duì)設(shè)計(jì)進(jìn)行了成功的系統(tǒng)仿真和綜合;同時(shí)還簡(jiǎn)單介紹了ASIC設(shè)計(jì)的整個(gè)流程。

關(guān)鍵詞: Verilog HDL 系統(tǒng)仿真 邏輯綜合 數(shù)字電子系統(tǒng)

日歷時(shí)鐘芯片" title="時(shí)鐘芯片">時(shí)鐘芯片應(yīng)用非常廣泛,例如在IC卡電子門(mén)鎖中,可利用日歷時(shí)鐘芯片的定時(shí)時(shí)鐘計(jì)數(shù)功能,在IC卡內(nèi)輸入客人住房時(shí)的時(shí)間段,只有當(dāng)時(shí)間段所包含的時(shí)間與日歷時(shí)鐘所記錄的時(shí)間一致時(shí),方可開(kāi)門(mén),否則IC卡為無(wú)效卡。

利用Synopsys公司提供的集成電路設(shè)計(jì)工具VCS和DC,設(shè)計(jì)了一個(gè)帶有48字節(jié)RAM的日歷時(shí)鐘芯片,包括該芯片RTL級(jí)代碼的編寫(xiě)、功能仿真和綜合,達(dá)到了預(yù)期的目標(biāo)。該芯片的具體性能指標(biāo)是:工作電源電壓為2.5~6V;日歷時(shí)鐘工作電源和RAM數(shù)據(jù)保持電源電壓為1~6V;工作電流最大為50μA;四年日歷時(shí)鐘,24或12小時(shí)格式,32.768kHz時(shí)基;48字節(jié)RAM,自動(dòng)字節(jié)地址增量;具有可編程的鬧鐘、定時(shí)和中斷功能。

1 ASIC設(shè)計(jì)概述

隨著深亞微米技術(shù)的發(fā)展,數(shù)字集成電路的規(guī)模已經(jīng)發(fā)展到上百萬(wàn)門(mén)。未來(lái)的二十多年里,一塊ASIC芯片中將會(huì)達(dá)到上千萬(wàn)門(mén)的規(guī)模。這樣的電路規(guī)模,仿真和綜合優(yōu)化在開(kāi)發(fā)過(guò)程中越來(lái)越重要。較復(fù)雜的數(shù)字電子系統(tǒng)設(shè)計(jì)往往采用自頂向下(Top-Down)的方法,設(shè)計(jì)流程可以分為以下幾個(gè)主要的部分:系統(tǒng)級(jí)設(shè)計(jì)" title="系統(tǒng)級(jí)設(shè)計(jì)">系統(tǒng)級(jí)設(shè)計(jì)、設(shè)計(jì)實(shí)現(xiàn)、設(shè)計(jì)驗(yàn)證和流片封裝。深亞微米工藝下的ASIC設(shè)計(jì)流程[2]如圖1所示。

本文主要介紹芯片的系統(tǒng)級(jí)設(shè)計(jì)和所有邏輯設(shè)計(jì),生成可供物理設(shè)計(jì)的經(jīng)過(guò)驗(yàn)證的門(mén)級(jí)網(wǎng)表文件。

2 芯片的系統(tǒng)級(jí)設(shè)計(jì)

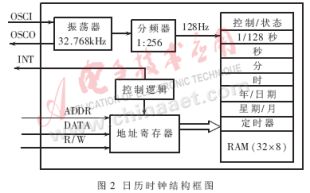

系統(tǒng)級(jí)設(shè)計(jì)是芯片設(shè)計(jì)的第一步,也是關(guān)鍵的一步。首先根據(jù)設(shè)計(jì)要求提出設(shè)計(jì)構(gòu)想,然后再對(duì)這一構(gòu)想進(jìn)行細(xì)化。本設(shè)計(jì)把整個(gè)系統(tǒng)分成幾大模塊,即產(chǎn)生32.768kHz的振蕩器(這個(gè)模塊不用設(shè)計(jì))、256分頻器、48字節(jié)RAM和地址寄存器。設(shè)計(jì)構(gòu)想如圖2所示。

RAM中的00~0FH單元是一些帶有特殊功能的寄存器,00H單元是控制芯片所有功能和操作的狀態(tài)寄存器,通過(guò)設(shè)置狀態(tài)寄存器,可以選擇32.768kHz時(shí)鐘模式或計(jì)數(shù)模式。在日歷時(shí)鐘模式中,1/128秒、秒、分、小時(shí)、年/日期、星期/月都是以BCD碼分別存放在01H~06H單元的寄存器中;而在事件計(jì)數(shù)模式中,則對(duì)輸入到振蕩器輸入端(OSCI)的脈沖計(jì)數(shù),事件計(jì)數(shù)器為6位BCD碼。07H單元是能存儲(chǔ)最大數(shù)為99天的定時(shí)器。08H是控制定鬧、定時(shí)和中斷輸出功能的鬧鐘控制寄存器。09H~0FH單元是以時(shí)鐘計(jì)數(shù)器相同的順序排列的鬧鐘寄存器。10FH~2FH單元用于儲(chǔ)存用戶信息。

對(duì)于這樣的設(shè)計(jì),傳統(tǒng)的方法是使用中小規(guī)模集成電路來(lái)構(gòu)成,本文則用Verilog HDL描述來(lái)實(shí)現(xiàn)。整個(gè)芯片采用模塊化設(shè)計(jì)方式和Top-Down設(shè)計(jì)方法,根據(jù)寄存器的不同劃分成模塊,然后用測(cè)試程序" title="測(cè)試程序">測(cè)試程序TestBench對(duì)頂層模塊進(jìn)行仿真;仿真通過(guò)后利用廠家提供的工藝庫(kù)及時(shí)序約束腳本文件對(duì)其進(jìn)行綜合;綜合通過(guò)后生成門(mén)級(jí)網(wǎng)表文件,然后再用廠家提供的仿真庫(kù)對(duì)門(mén)級(jí)網(wǎng)表進(jìn)行綜合后仿真。本文設(shè)計(jì)用到的工藝庫(kù)是臺(tái)灣旺宏公司(Macronix, MXIC)提供的基本單元庫(kù)(slow.db和fast.db)、基本符號(hào)單元庫(kù)(slow.sdb)和用于綜合后仿真的庫(kù)文件仿真庫(kù)(models.v)。

這是一個(gè)同步時(shí)序電路的設(shè)計(jì),所以保證正確的時(shí)序是設(shè)計(jì)的關(guān)鍵,本設(shè)計(jì)中有四個(gè)時(shí)鐘:

(1)系統(tǒng)時(shí)鐘clksys,是外部微控制器提供的時(shí)鐘信號(hào)" title="時(shí)鐘信號(hào)">時(shí)鐘信號(hào),用作寄存器讀、寫(xiě)時(shí)鐘信號(hào);

(2)測(cè)試時(shí)鐘clktest,是整個(gè)芯片的測(cè)試時(shí)鐘信號(hào),一般限于廠家使用。

(3)時(shí)基時(shí)鐘clk32,定時(shí)方式時(shí),外部石英晶振提供的32.768kHz振蕩信號(hào)經(jīng)過(guò)256分頻后得到時(shí)鐘信號(hào)(evt128),作為RAM前16字節(jié)特殊寄存器的同步時(shí)鐘信號(hào)。

(4)計(jì)數(shù)時(shí)鐘clkevt,計(jì)數(shù)模式時(shí)的外部計(jì)數(shù)脈沖信號(hào)。

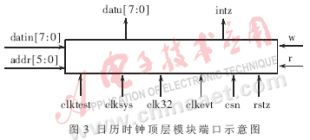

圖3是日歷時(shí)鐘頂層模塊端口示意圖,讀選通信號(hào)w、寫(xiě)選通信號(hào)r、片選信號(hào)csn和RAM地址控制信號(hào)addr[5:0]是由外部微處理器提供的。當(dāng)寫(xiě)信號(hào)w為真時(shí),將輸入數(shù)據(jù)datin[7:0]寫(xiě)入存儲(chǔ)器被選中的地址;當(dāng)讀信號(hào)r為真時(shí),將從存儲(chǔ)器被選中的地址中輸出數(shù)據(jù)datu[7:0]。當(dāng)滿足下面兩個(gè)條件之一時(shí),中斷請(qǐng)求信號(hào)intz輸出低電平:① 00H單元中第1位為1,并且起鬧控制寄存器的第7位為1;②00H單元中的第0位為1,并且08H單元的第3位為1。

由于篇幅有限,在這里只寫(xiě)出頂層模塊rtc的部分設(shè)計(jì)程序,具體如下:

`timescale 10ns/10ps //模擬時(shí)間定標(biāo);

module rtc (clktest,clksys,clk32,clkevt,csn,rstz,w,r, addr, datin, datu, intz) ;

input clktest,clksys,clk32,clkevt,csn,rstz,w,r; //輸入輸出端口說(shuō)明;

input [7:0] datin;

input [5:0] addr;

output [7:0] datu;

output intz;

reg [7:0] datu; //設(shè)定變量的數(shù)據(jù)結(jié)構(gòu);

ctl_status c0 ( clksys, evt128, rstz, w, cs00,…… );//調(diào)用00H單元子模塊;

sec128 c1 ( clksys, clktest, evt128, rstz,……); //調(diào)用01H單元子模塊;

sec c2 ( clksys, evt128, clktest, rstz,……);//調(diào)用02H單元子模塊;

……

int c20 (timer_flag, alarm_flag,……);//調(diào)用產(chǎn)生中斷模塊;

always @ ( addr or stop_soft or ) begin

if ( cs & r ) begin //根據(jù)控制地址信號(hào)而輸出RAM中各寄存器的數(shù)據(jù);

case ( addr)

0 :datu = { stop_soft, hold_flag, func_mode,mask_flag, alarm_en, alarm_flag, time_flag};

1 :datu = data_latch[7:0];

2 :datu = data_latch[15:8];

……

47:datu = data_ram [255:248];

default:datu = 8`h00;

endcase

end

else

datu = 8`h00;

end

endmodule

在頂層模塊中調(diào)用了根據(jù)不同功能而編寫(xiě)的20個(gè)子模塊,如ctl_status.v、sec128.v、sec.v和ram.v等。其中RAM存儲(chǔ)器的1F~2FH單元是模擬電路,要用全定制的方法生成。而在數(shù)字集成電路設(shè)計(jì)中,仿真時(shí)經(jīng)常要用到存儲(chǔ)器的行為模型,這里給出的行為模型ram.v用于仿真。

3 利用EDA工具進(jìn)行系統(tǒng)仿真

設(shè)計(jì)人員利用先進(jìn)的EDA工具作為測(cè)試平臺(tái),以驗(yàn)證數(shù)字電子系統(tǒng)設(shè)計(jì)模塊的邏輯功能和時(shí)序功能。雖然不同的EDA工具提供的平臺(tái)不同,但都可以對(duì)被測(cè)試對(duì)象加載激勵(lì)信號(hào),并通過(guò)波形輸出、文件記錄輸出等方式觀察和比較仿真結(jié)果。加載激勵(lì)信號(hào)需要設(shè)計(jì)人員設(shè)計(jì)測(cè)試程序(TestBench)[3],對(duì)于較大規(guī)模的系統(tǒng)設(shè)計(jì),測(cè)試程序的設(shè)計(jì)有時(shí)比本身的程序設(shè)計(jì)還要復(fù)雜。

在本文的設(shè)計(jì)中,首先對(duì)每一個(gè)子模塊設(shè)計(jì)一個(gè)測(cè)試程序,單獨(dú)進(jìn)行邏輯仿真,然后再設(shè)計(jì)一個(gè)測(cè)試程序?qū)φ麄€(gè)設(shè)計(jì)進(jìn)行邏輯仿真。由于篇幅有限,在這里僅寫(xiě)出sec.v的部分測(cè)試程序,具體如下:

`timescale 10ns/10ps

module sec_test;

reg clksys,evt128,clktest,carry_sec128,rstz,datin,datout,w;

reg [7:0] datin, datout;

reg [1:0] func_mode;

sec c2 ( clksys, evt128, clktest, carry_sec128, rstz, datin,

datout, func_mode, w, );

always #10 clksys = ~ clksys;

always #30 evt128 = ~ evt128;

always #50 clktest = ~ clktest;

always #80 carry_sec128 = ~ carry_sec128; //產(chǎn)生輸入激勵(lì);

initial

begin

rstz = 0;

#90 rstz = 1;

end //產(chǎn)生復(fù)位信號(hào)

initial

begin

w = 0;

#100 w = 1;

#5 w = 0;

#1100 w = 1;

#5 w = 0;

end //產(chǎn)生寫(xiě)信號(hào);

initial

begin

func_mode = 0;

#1000 func_mode = 1;

end //功能模式的選擇;

initial

begin

datin = 0;

#20 datin = 00100101h;

#1000 datin = 00010010;

end //輸入數(shù)據(jù);

always @ (func_mode or datin or datout)

$ display ('At time %t, func_mode=%b, datin is %b%b, datout is %b', $time, func_mode, datin, datout );//輸出模擬結(jié)果。

利用Synopsys公司的仿真工具VCS進(jìn)行仿真,無(wú)論在功能上還是在時(shí)序上,都完全符合要求。

4 利用EDA工具進(jìn)行綜合和優(yōu)化

綜合是利用芯片制造商提供的基本電路單元(綜合庫(kù))實(shí)現(xiàn)用硬件描述語(yǔ)言描述的電路功能。現(xiàn)在許多優(yōu)秀的綜合工具都能借助現(xiàn)有的綜合庫(kù)將Verilog HDL源代碼進(jìn)行綜合,轉(zhuǎn)化成門(mén)級(jí)電路圖,并且可以根據(jù)設(shè)計(jì)者施加的約束條件對(duì)電路進(jìn)行優(yōu)化,產(chǎn)生面積或者速度達(dá)到最優(yōu)的結(jié)構(gòu),并生成相應(yīng)的邏輯網(wǎng)表以供后端設(shè)計(jì)使用。

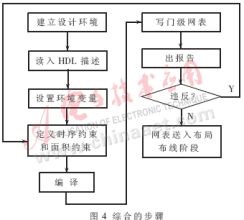

綜合時(shí)要進(jìn)行延時(shí)計(jì)算和設(shè)計(jì)規(guī)則檢查,需要設(shè)置的相關(guān)內(nèi)容主要包括:操作環(huán)境、導(dǎo)線負(fù)載模型、設(shè)計(jì)約束、設(shè)計(jì)規(guī)則約束。通常情況,設(shè)計(jì)者要先編輯一個(gè)包括這些設(shè)置的腳本文件(例如本文編輯的腳本文件rtc.tcl),啟動(dòng)邏輯綜合工具DC后就可,執(zhí)行文件中的各條指令了。綜合的過(guò)程如圖4所示。下面利用日歷時(shí)鐘實(shí)例簡(jiǎn)單介紹這一過(guò)程。

(1) 建立設(shè)計(jì)環(huán)境

臺(tái)灣旺宏公司的0.35μm CMOS標(biāo)準(zhǔn)單元綜合庫(kù)slow.db和fast.db包含了與非、或非、非門(mén)等基本邏輯單元,還有選擇器、與或非、或與非等較復(fù)雜的組合邏輯以及DFF(D觸發(fā)器)等時(shí)序邏輯單元。利用該庫(kù)可以這樣來(lái)建立環(huán)境:

set target_library {slow.db fast.db}

set link_library {* slow.db fast.db}

set search_path '/home/tools/synopsys /library'

(2) 讀入HDL描述

如果讀入多個(gè)模塊,首先應(yīng)該讀入的是頂層模塊。要將當(dāng)前的設(shè)計(jì)設(shè)置為頂層模塊,可以這樣來(lái)設(shè)置:

read_verilog 'home/design/rtl/rtc.v'

read_verilog 'home/design/rtl/sec.v'

current_design rtc

(3) 定義環(huán)境變量

環(huán)境變量輸出網(wǎng)表和輸出報(bào)告等路徑設(shè)置可以這樣來(lái)定義:

netlist_path = 'home/design/netlist'

report_path = 'home/design/report'

(4) 定義性能約束、時(shí)序約束和面積約束

性能約束主要包括創(chuàng)建時(shí)鐘、輸入延遲和輸出延遲等;綜合的目標(biāo)是得到最小的面積。可以這樣來(lái)設(shè)置:

creat_clock-period 70-name my_clock [get_ports clksys]

set ex_clk[remove_from_collection[all_inputs] [get_ports clksys]

set_input_delay 4 -clock my_clock $ex_clk

set_output_delay 3 -clock my_clock [all_outputs]

set_max_area 1

(5)編譯

用compile命令進(jìn)行編譯即可。

(6)寫(xiě)門(mén)級(jí)網(wǎng)表

綜合后的門(mén)級(jí)網(wǎng)表可以用edif文件形式保存,也可以用.V文件形式存放,采用如下命令:

write-format verilog-hierarchy-output $netlist_path/rtc.vg

此外,還需要保存延時(shí)信息,以便綜合后仿真,延時(shí)信息一般放在.sdf文件中,采用如下命令:

write_sdf $netlist_path/rtc.sdf -version 1.4

(7)給出報(bào)告

可以報(bào)告綜合出的面積、時(shí)序信息、違反約束路徑以及單元的個(gè)數(shù)等,并存放到定義的目錄文件中,下面舉幾個(gè)例子:

report_area > $report_path/area.rpt

report_timing > $report_path/timing.rpt

report_constraint -verbose -all_violators > $report_path/constrain.rpt

利用Synopsys公司的邏輯綜合工具DC[4]進(jìn)行綜合和優(yōu)化非常成功。

本文設(shè)計(jì)主要描述帶有48字節(jié)RAM的日歷時(shí)鐘芯片的邏輯設(shè)計(jì)過(guò)程,并對(duì)其成功地進(jìn)行了代碼編寫(xiě)、仿真和綜合,生成的網(wǎng)表完全可以送給后端工程師進(jìn)行布局布線、版圖設(shè)計(jì)等。當(dāng)然,本邏輯設(shè)計(jì)不是一蹴而就的。在此過(guò)程中,對(duì)各種異常情況都需要認(rèn)真分析和反復(fù)調(diào)試。

參考文獻(xiàn)

1 Design Automation Standards Committee of the IEEE Com-puter Society. USA: IEEE Standard Hardware Description Language Based on the Verilog Hardware Description Lan-guage IEEE Std: 1364~1995

2 Chaudhry H K, Eichenberger P, Chowdhury D R. Mixed 2-4 state Simulation with VCS. Verilog HDL Conference,1997,IEEE International, 31 March-2 April 1997: 77~82

3 任艷穎,王 彬.IC設(shè)計(jì)基礎(chǔ).西安:西安電子科技大學(xué)出版社,2003

4 The SOLD of Synopsys. Design Compiler User Guide.Synopsys, 2003

5 王長(zhǎng)宏,陳朝陽(yáng),鄒雪城,應(yīng)建華.Verilog HDL設(shè)計(jì)實(shí)例及其仿真與綜合.計(jì)算機(jī)應(yīng)用,2001;27(12)