摘 要: 介紹一種提高直接數字合成器(DDS)系統時鐘頻率的并行處理方法。給出了一個基于現場可編程門陣列(FPGA)的具有400MHz系統時鐘頻率DDS電路的實現方法和實驗測試結果。采用直接中頻輸出方式,輸出頻率范圍250MHz~350MHz,頻率分辨率6Hz,寄生信號抑制50dB。該DDS電路具有接口簡單、使用靈活等優點,可用于雷達、電子戰領域的寬帶信號產生。

關鍵詞: 直接數字合成(DDS) 現場可編程門陣列(FPGA) 寬帶 并行處理

直接數字合成器(DDS)不僅能提供精細的頻率分辨率、更高的頻率轉換速度和良好的相位噪聲,而且容易實現各種調制功能,如頻率調制、相位調制、幅度調制等。因此,DDS在雷達、通信和電子戰等系統中得到了極其廣泛的應用。隨著現場可編程門陣列(FPGA)技術的發展,為了更加充分地利用DDS的優點,并簡化系統的接口和控制,提高系統的整體性能和工作可靠性,為進一步實現系統集成創造條件,利用ASIC和FPGA實現DDS電路的思想早已受到了重視并取得了進展[1][2]。

不同的應用領域,對DDS的性能有不同的要求。當把DDS用做雷達系統中的本振信號源時,對寄生信號抑制的要求可能比較高,如要求在60dB或70dB以上。當把DDS用于雷達干擾系統時,除了對寄生信號抑制有一定的要求外,更重要的是其產生寬帶信號的能力。為了產生寬帶信號,要求DDS的系統時鐘頻率要高。盡管目前FPGA的速度和規模都已經達到了相當高的水平,但與電子干擾系統對它的要求相比仍有差距。按照目前FPGA的技術水平及使用經驗,系統時鐘選擇200MHz是一個比較合理的選擇。因此,為了滿足電子干擾系統更高(如400MHz系統時鐘)的要求,應該采用并行處理技術。

1 并行DDS電路工作原理

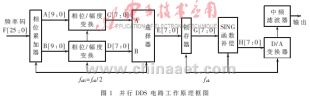

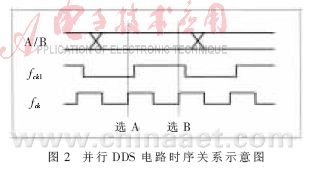

圖1所示為并行DDS電路工作原理框圖,主要包括:相位累加器、兩路相位/幅度變換電路、二選一選擇器、鎖存器、SINC函數補償濾波器、D/A變換器和中頻濾波器。相位累加器通過對輸入頻率碼的累加,產生A、B兩路相位累加輸出,其中A路信號在前,B路信號在后(兩路信號合成一路信號后)。兩路相位/幅度變換電路分別對兩路相位累加器輸出的相位進行相位/幅度變換,獲得兩路幅度輸出。然后由二選一選擇器將兩路信號合并成一路信號(S=0時選A,S=1時選B)。相位累加器、相位/幅度變換電路的時鐘以及選擇器選擇端S的信號為fck1,它是由DDS電路系統時鐘fck分頻得到,即fck1=fck/2。而選擇器后面的鎖存器以及SINC函數補償濾波器、D/A變換器的時鐘為系統時鐘。為了簡化電路實現,采用直接中頻方法取出D/A變換器的中頻信號輸出,同時,為了補償D/A變換輸出信號幅度隨頻率增加引起的衰減,圖1中增加了SINC函數補償濾波器。圖2給出了fck1、fck與數據之間時序關系的示意圖。

2 并行DDS電路實現

主要介紹相位累加器電路和相位/幅度變換器電路的實現。

2.1 相位累加器電路實現

實現并行相位累加器的直接方法是:由兩套結構完全相同的相位累加器電路構成,相位累加器的輸入(頻率碼)也相同,只是兩路輸出要有一個固定的初始相位偏差,其數值為相位累加器輸入(頻率碼)的1/2。

為了電路實現容易,需對上述方法進行簡化。這里提供一種較為簡單的方法,即利用一個相位累加器產生第一路(A路)相位累加器輸出,而另一路相位累加器輸出通過將第一路輸出的相位與相位累加器輸入(頻率碼)的1/2相加得到,如圖3所示。在圖3中,假定系統時鐘為400MHz,假定輸入的頻率碼為26位,范圍為F[25:0],其中位25代表200MHz,位24代表100MHz,…,位0為最低有效位,也就是DDS的分辨率fck/226=5.96Hz。

相位累加器電路中各器件的時鐘頻率為fck1=200MHz。相位累加器的輸入取26位頻率碼F[25:0]的低25位F[24:0],即得到A路相位累加器的輸出為A[24:0]。F[25:0]的高25位F[25:1]經右移一位(相當于乘1/2)得到C[24:0]后與A路相位累加器的輸出A[24:0]相加得到B路相位累加器的輸出B[24:0]。

最后,為了減小后面相位/幅度變換電路的硬件量,鎖存器只取出用于進行相位/幅度變換所需位數的相位(相位截斷),這里取相位截斷輸出為10位,A路為G[9:0],B路為H[9:0]。

2.2 相位/幅度變換器電路實現

相位/幅度變換電路的功能是把由相位累加器輸出的相位信息轉換成幅度信息。相位/幅度變換電路通常采用ROM電路實現,但也可采用數字邏輯電路實現。

并行相位/幅度變換器由兩套結構完全相同的相位/幅度變換器構成,因此,下面只介紹其中的一個。相位/幅度變換的原理可以很容易由ROM構成的查找表(LUT)理解。相位/幅度變換的內容存儲在ROM中,以相位值作為ROM的地址,ROM的輸出作為變換后的幅度。

與相位累加器不同,相位/幅度變換器的硬件量隨相位位數(ROM地址)的增加指數增加,而相位累加器硬件量隨累加器位數的增加線性增加。因此,當相位位數(影響DDS的寄生信號性能)較大時,所需硬件量將急劇增加。盡管前面已經對相位進行了截斷,但為了保證所需的寄生信號性能,剩下的用于進行相位/幅度變換的相位位數仍然較大,如果直接實現所需硬件量仍然較大。

下面兩種方法對減小硬件量比較有效。一是根據SIN函數的對稱性,只需要對一個象限進行相位/幅度變換,另外三個象限可以經變換獲得,這樣可節省近3/4的硬件量[3];第二種是采用分段線性化的方法,也可有效降低ROM地址的位數[4]。

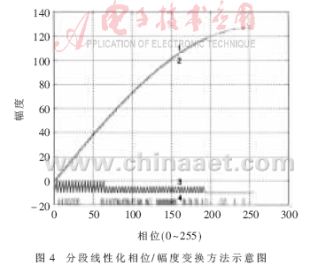

以一個10位相位/8位幅度的相位/幅度變換電路為例,介紹相位/幅度變換電路的具體實現方法并分析硬件量節省的情況。圖4是分段線性化相位/幅度變換方法示意圖。曲線1是用于進行相位/幅度變換的原始正弦信號前1/4周期(第一象限)的曲線,將它分解成下面的3條曲線(曲線2、3、4)。曲線2是粗相位/幅度變換對應的曲線。曲線3和4分別對應的是線性變化部分(只有0、1、2三個值,即2位)和校正部分(只有0、1兩個值,即1位)。注意,為了清楚,曲線3和4的幅度都放大了5倍,并分別下移10和20。

根據圖4的方法,圖5給出了相位/幅度變換電路原理框圖。相位輸入10位,幅度輸出8位,分析中假定忽略掉兩組異或門和一個加法器所占用的硬件資源。在不采用任何措施以節省硬件資源的情況下,地址為10位,輸出幅度為7位(幅度的最高有效位不需要ROM資源),所需硬件量(ROM容量)為:210×7=7168。當利用SIN函數的對稱性只對第1象限進行相位/幅度變換時,地址由10位變成了8位,所需硬件量變為:28×7=1792,減小了75%。在第1象限的相位/幅度變換中進一步采用分段線性化的方法,將一個較大的ROM(地址8位,字長7位)分解成三個較小的ROM:一個粗相位/幅度變換(地址6位,字長7位),一個分段線性變化部分(它只與最高兩位和最低兩位地址有關,地址4位,字長2位),還有一個校正部分(地址8位,字長1位)。因此,所需硬件總容量變為:26×7+24×2+28×1=736,又減小了近59%。可見,綜合采用上述兩種方法,可以使相位/幅度變換所需的硬件量大幅度減小。

根據具體情況和具體要求的不同,分解方法并不局限于上面介紹的方法。以圖5為例,由于線性變化部分和校正部分都較小,因此也可以將二者合并成一個地址8位、字長2位的校正部分,這時,所需硬件總容量為:26×7+28×2=960,減小的硬件量為46%。

3 實驗測試結果

為了滿足電子干擾系統對寬帶信號產生的需要,按照上述方法設計并實現了一個基于FPGA的并行DDS樣機,系統時鐘400MHz(兩路200 MHz構成),輸出頻率范圍250MHz~350MHz,頻率分辨率6Hz,相位截斷10位,D/A變換器幅度分辨率8位。

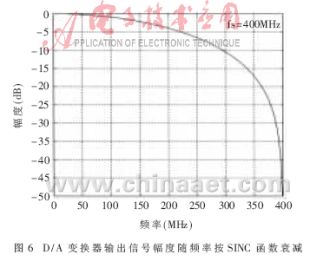

為了簡化外部電路,采用了直接中頻輸出的方法,即直接取出頻率范圍250MHz~350MHz的信號。由圖6可以看出,由于D/A變換器輸出信號幅度隨頻率按SINC函數衰減,在輸出信號250MHz~350MHz頻率范圍內,幅度變化范圍較大,約為(-6.5)~(-17.1)=10.6dB。因此,電路中還包含了SINC函數補償濾波器。

根據文獻[5],10位相位/8位幅度DDS的最高寄生信號抑制為-60.2dB。不過,這只是在特定條件下的理想結果,實際的DDS寄生信號性能還受到采樣信號頻譜折疊、D/A變換器采樣脈沖不理想(不是理想的沖擊脈沖)等因素的影響。特別是當輸出信號頻率較高時,D/A變換器非線性的影響更不能忽視。因此,實際測量結果與理論分析會有所不同。圖7給出的是基于FPGA的并行DDS樣機的輸出信號頻譜分布測量結果,輸出信號約為300MHz,測量范圍是在信號附近(span=1MHz),此時的最大寄生信號抑制優于50dB。

本文介紹了一種通過采用并行處理技術提高DDS系統時鐘的方法,給出了一個基于FPGA的400MHz系統時鐘DDS電路的實現方法和測試結果,輸出信號頻率范圍250MHz~350MHz,頻率分辨率6Hz,寄生信號抑制優于50dB,為實現雷達和電子戰等領域中的寬帶信號產生提供了一種可供選擇的方案,具有實用性。

參考文獻

[1] SALOUS S.An ASIC solution for programming digital synthesizers for the generation of spread spectrum signals,Fifth bangor symposium on communications.

[2] 周國富.利用FPGA實現線性調頻DDS專用電路.現代雷達,1997,19(6):95-99.

[3] Tierney.A digital frequency synthesizer.IEEE Trans.AEV,1971,19(1):48-57.

[4] 周國富.一種基于算法的相位/幅度變換方法.第二屆DDS技術與應用研討會論文集(合肥).2001,5.

[5] 周國富.相位量化數字射頻存儲器的寄生信號性能分析,電子學報,2005,33(12):26-31.

[6] 郭延延,李敬,唐昆.多相結構采樣率變換器的FPGA實現.電子技術應用,2006,32(9):97-100.