文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.019

中文引用格式: 魏麗玲,朱平,石永亮. 基于FPGA的圖像采集與存儲(chǔ)系統(tǒng)設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2015,41(11):67-69,73.

英文引用格式: Wei Liling,Zhu Ping,Shi Yongliang. Design of image capture and storage system based on FPGA[J].Application of Electronic Technique,2015,41(11):67-69,73.

0 引言

隨著科學(xué)技術(shù)的發(fā)展,視覺(jué)技術(shù)被廣泛應(yīng)用于軍事、工業(yè)以及測(cè)控領(lǐng)域。視覺(jué)是人們主要的信息源,通過(guò)圖像采集系統(tǒng)對(duì)周?chē)h(huán)境圖像數(shù)據(jù)進(jìn)行采集,這樣機(jī)器能夠替代人類(lèi)獲得環(huán)境信息,此種系統(tǒng)被廣泛應(yīng)用于測(cè)控系統(tǒng),以獲得飛行器的環(huán)境參數(shù)。利用高性能的FPGA控制圖像數(shù)據(jù)的采集與圖像數(shù)據(jù)處理,通過(guò)交錯(cuò)雙平面技術(shù)對(duì)處理后的圖像數(shù)據(jù)進(jìn)行存儲(chǔ),通過(guò)USB總線(xiàn),將處理后的數(shù)據(jù)傳輸給上位機(jī)進(jìn)行解包并顯示。

1 系統(tǒng)的總體設(shè)計(jì)

系統(tǒng)工作過(guò)程:采集存儲(chǔ)模塊的FPGA通過(guò)模擬IIC時(shí)序,對(duì)CMOS模擬傳感器進(jìn)行初始化與配置,并采集圖像數(shù)據(jù),通過(guò)信號(hào)調(diào)理電路將采集的模擬信號(hào)進(jìn)行濾波放大,并將調(diào)理放大的信號(hào)進(jìn)行A/D轉(zhuǎn)換后輸出給FPGA,F(xiàn)PGA將接收的數(shù)據(jù)通過(guò)內(nèi)部FIFO緩存后傳輸給Flash芯片進(jìn)行存儲(chǔ)。FPGA回讀Flash芯片內(nèi)的數(shù)據(jù),通過(guò)LVDS總線(xiàn)(型號(hào)DS92LV1023)發(fā)送給監(jiān)控讀數(shù)模塊,通過(guò)USB接口(型號(hào)CY7C68013)傳輸給上位機(jī),由上位機(jī)對(duì)圖像進(jìn)行解碼顯示。系統(tǒng)的原理框圖如圖1所示。

FPGA采用XILINX公司的XC3S1400AN,內(nèi)部包含有豐富的RAM資源,便于數(shù)據(jù)采集[1-3]。

2 CMOS圖像數(shù)據(jù)采集模塊

通過(guò)FPGA對(duì)CMOS圖像采集模塊進(jìn)行邏輯控制。其中采集模塊主要完成對(duì)視頻圖像的采集,對(duì)采集到的信號(hào)進(jìn)行模數(shù)轉(zhuǎn)換,并對(duì)此信號(hào)進(jìn)行低通濾波及放大后[4-7]傳輸給圖像數(shù)據(jù)存儲(chǔ)模塊進(jìn)行存儲(chǔ)。

在本文的系統(tǒng)設(shè)計(jì)中,對(duì)圖像數(shù)據(jù)的采集是核心模塊。視頻前端應(yīng)用CMOS圖像傳感器(型號(hào)OV7670),輸出的圖像數(shù)據(jù)最高為30幀/s,30萬(wàn)像素,芯片內(nèi)部的寄存器達(dá)201個(gè),通過(guò)FPGA控制單片機(jī)對(duì)傳感器寄存器進(jìn)行配置。單片機(jī)采用IIC總線(xiàn)為傳感器寄存器串行傳輸數(shù)據(jù),在對(duì)IIC總線(xiàn)時(shí)序控制中,利用54個(gè)SDA時(shí)鐘傳輸32 bit的配置數(shù)據(jù),其中前兩個(gè)時(shí)鐘周期完成時(shí)序模塊的初始化,延時(shí)4個(gè)周期后,啟動(dòng)串行數(shù)據(jù)的傳輸,傳送完一個(gè)字節(jié)數(shù)據(jù)后等待從接收器(CMOS圖像傳感器)的應(yīng)答信號(hào),當(dāng)單片機(jī)確定從接收器正確接收后,啟動(dòng)發(fā)送下一個(gè)字節(jié)的配置數(shù)據(jù),直到發(fā)送完4個(gè)字節(jié)的配置數(shù)據(jù)后,發(fā)送終止信號(hào),結(jié)束IIC總線(xiàn)的傳輸,完成傳感器的初始化,從而控制圖像數(shù)據(jù)的質(zhì)量、圖像數(shù)據(jù)的制式以及數(shù)據(jù)的傳輸方式。其中IIC總線(xiàn)傳輸模塊的時(shí)鐘為30 kHz。

CMOS圖像傳感器將采集到的光信號(hào)轉(zhuǎn)換為模擬信號(hào),被轉(zhuǎn)換的模擬信號(hào)很微弱,為達(dá)到A/D轉(zhuǎn)換芯片對(duì)處理信號(hào)電平的要求,需要對(duì)傳感器輸出的模擬信號(hào)進(jìn)行放大處理,經(jīng)A/D轉(zhuǎn)換芯片將模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)輸出。FPGA的解碼部分通過(guò)控制3種同步信號(hào)(像素時(shí)鐘同步信號(hào)、行同步信號(hào)和場(chǎng)同步信號(hào)),進(jìn)而得到8 bit的RGB制式的圖像數(shù)據(jù)信號(hào)。圖像傳感器的分辨率為640×480,行同步信號(hào)為“1”時(shí)有效,每行顯示的有效數(shù)據(jù)是640 bit;每列顯示的有效數(shù)據(jù)是480 bit,場(chǎng)同步信號(hào)為“0”時(shí)輸出轉(zhuǎn)化后的有效數(shù)據(jù),當(dāng)其變?yōu)椤?”時(shí),表明一幀圖像數(shù)據(jù)傳輸完成。采集到的數(shù)據(jù)通過(guò)FPGA芯片的內(nèi)部FIFO緩存。

3 圖像數(shù)據(jù)存儲(chǔ)模塊

本文采用的FPGA片內(nèi)存儲(chǔ)器有限,考慮到大數(shù)據(jù)量的圖像數(shù)據(jù),需要外部擴(kuò)展存儲(chǔ)器,選用K9WBG08U1M型號(hào)的Flash,此Flash最大存儲(chǔ)4 GB圖像數(shù)據(jù),以頁(yè)為單位對(duì)數(shù)據(jù)進(jìn)行讀寫(xiě),以塊為單位對(duì)數(shù)據(jù)進(jìn)行擦除,包含3種地址控制信號(hào)(列地址、行地址和塊地址)。圖像存儲(chǔ)模塊在上電初始化后,F(xiàn)PGA控制時(shí)序擦除Flash內(nèi)存,并等待存儲(chǔ)視頻前端采集到的圖像數(shù)據(jù)。采用交錯(cuò)雙平面式對(duì)接收到的圖像數(shù)據(jù)進(jìn)行存儲(chǔ),將1片4 GB的Flash分成2片2 GB的Flash,對(duì)其中一片F(xiàn)lash進(jìn)行寫(xiě)操作的同時(shí)對(duì)另一片F(xiàn)lash進(jìn)行讀操作,此種交錯(cuò)方式使輸入輸出不間斷,實(shí)現(xiàn)圖像數(shù)據(jù)的無(wú)縫處理,提高數(shù)據(jù)傳輸與處理的效率。

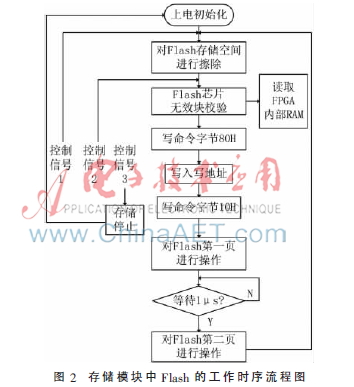

為了方便對(duì)圖像數(shù)據(jù)進(jìn)行讀寫(xiě)操作,引入3種控制信號(hào):地址使能信號(hào)、命令使能信號(hào)和數(shù)據(jù)鎖存信號(hào)。在FPGA的邏輯時(shí)序控制中,當(dāng)?shù)刂肥鼓苄盘?hào)有效為“0”時(shí),F(xiàn)PGA的8個(gè)I/O口并行輸出地址,在對(duì)Flash芯片進(jìn)行尋址時(shí)寫(xiě)入32 bit地址(13 bit是字節(jié)地址,19 bit是頁(yè)地址和塊地址),分5次輸出;當(dāng)命令使能信號(hào)有效為“0”時(shí),8位I/O口輸出命令,當(dāng)數(shù)據(jù)鎖存信號(hào)有效為“0”時(shí),8位I/O口輸入8 bit圖像數(shù)據(jù)。圖2所示為Flash存儲(chǔ)模塊工作時(shí)序流程圖。

4 監(jiān)控讀數(shù)模塊

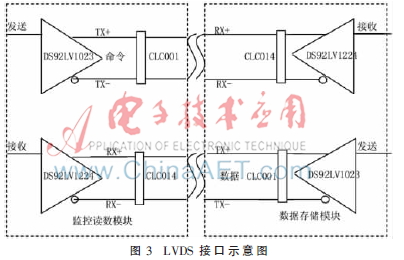

通過(guò)綜合考慮,圖像數(shù)據(jù)存儲(chǔ)模塊與監(jiān)控讀數(shù)模塊通過(guò)低壓差分傳輸方式(LVDS)進(jìn)行數(shù)據(jù)的傳輸,此種傳輸方式適用于高速短距離傳輸,但是,在利用普通雙絞線(xiàn)進(jìn)行數(shù)據(jù)的傳輸時(shí),信號(hào)的傳輸損耗隨著信號(hào)頻率的增加而增加。基于此種限制,在圖像數(shù)據(jù)的發(fā)送端加入驅(qū)動(dòng)以增強(qiáng)信號(hào),在圖像數(shù)據(jù)的接收端采用均衡補(bǔ)償法補(bǔ)償信號(hào)在傳輸過(guò)程中的損耗。

此監(jiān)控讀數(shù)模塊采用LVDS接口和422接口與圖像數(shù)據(jù)存儲(chǔ)模塊進(jìn)行通信。LVDS接口主要負(fù)責(zé)存儲(chǔ)命令的下發(fā)和回讀存儲(chǔ)模塊的圖像數(shù)據(jù),422接口主要負(fù)責(zé)對(duì)存儲(chǔ)模塊狀態(tài)的監(jiān)控,通過(guò)回讀存儲(chǔ)模塊的狀態(tài)信息以確定存儲(chǔ)模塊是否正常工作。圖3所示為監(jiān)控讀數(shù)模塊與數(shù)據(jù)存儲(chǔ)模塊的LVDS接口示意圖。存儲(chǔ)模塊接收到讀數(shù)命令,通過(guò)LVDS接口,將數(shù)據(jù)傳輸給監(jiān)控讀數(shù)模塊,監(jiān)控讀數(shù)模塊通過(guò)檢測(cè)數(shù)據(jù)的高兩位判斷是否為有效數(shù)據(jù)。若為有效數(shù)據(jù),將此數(shù)據(jù)存儲(chǔ)到外部的FIFO中,若為無(wú)效數(shù)據(jù),則丟棄。監(jiān)控讀數(shù)模塊向存儲(chǔ)模塊發(fā)送啟動(dòng)存數(shù)數(shù)據(jù)命令后,數(shù)據(jù)存儲(chǔ)模塊通過(guò)422接口將本身的狀態(tài)信息發(fā)送給數(shù)據(jù)監(jiān)控模塊,通過(guò)這些狀態(tài)信息能夠判斷存儲(chǔ)模塊是否正常工作。

5 系統(tǒng)測(cè)試結(jié)果

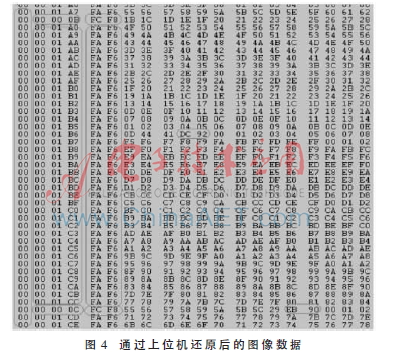

在對(duì)本系統(tǒng)的硬件和軟件模塊調(diào)試成功后,對(duì)系統(tǒng)的總體功能進(jìn)行測(cè)試。CMOS模擬傳感器對(duì)圖像數(shù)據(jù)進(jìn)行采集后,通過(guò)數(shù)據(jù)存儲(chǔ)模塊對(duì)采集到的數(shù)據(jù)進(jìn)行存儲(chǔ),由監(jiān)控讀數(shù)模塊通過(guò)LVDS接口回讀圖像數(shù)據(jù),并將此數(shù)據(jù)通過(guò)USB接口上傳給上位機(jī),上位機(jī)對(duì)此數(shù)據(jù)進(jìn)行解碼并顯示,圖4所示為還原后的圖像數(shù)據(jù)。其中FAF6為幀開(kāi)始標(biāo)志,幀標(biāo)志前面的3個(gè)字節(jié)是幀計(jì)數(shù)。

6 結(jié)論

本文利用CMOS傳感器實(shí)現(xiàn)了對(duì)圖像數(shù)據(jù)實(shí)時(shí)采集的要求。應(yīng)用K9WBG08U1M型號(hào)的Flash芯片通過(guò)交叉雙平面技術(shù)對(duì)此圖像數(shù)據(jù)進(jìn)行存儲(chǔ),實(shí)現(xiàn)了數(shù)據(jù)的無(wú)縫傳輸,以流水線(xiàn)的數(shù)據(jù)傳輸方式提高了本系統(tǒng)的傳輸效率。監(jiān)控讀數(shù)模塊通過(guò)LVDS接口和422接口對(duì)存儲(chǔ)模塊的數(shù)據(jù)進(jìn)行回讀并在上位機(jī)上顯示。系統(tǒng)充分利用了具有高性能的XC3S1400AN(所用FPGA型號(hào))芯片,提高了系統(tǒng)的運(yùn)行速度,具有很高的參考價(jià)值。

參考文獻(xiàn)

[1] 吳萌.一種高速、大容量圖像存儲(chǔ)系統(tǒng)設(shè)計(jì)[D].西安:中國(guó)科學(xué)院西安光學(xué)精密機(jī)械研究所,2009.

[2] 邢彥梅,董曉倩,張園.一種基于JPEG2000算法的圖像傳感器設(shè)計(jì)[J].電視技術(shù),2012,36(11):44-46.

[3] 王小艷,張會(huì)新,孫永生,等.Camera link協(xié)議和FPGA的數(shù)字圖像信號(hào)源設(shè)計(jì)[J].國(guó)外電子元器件,2008,16(7):59-61.

[4] 任偉,張彥軍,白先民.基于LVDS的高速數(shù)據(jù)傳輸裝置的設(shè)計(jì)[J].科學(xué)技術(shù)與工程,2012,12(29):7759-7763.

[5] 郭錚,劉文怡,馮妮.基于FPGA多通道高速數(shù)據(jù)采集存儲(chǔ)器設(shè)計(jì)[J].電視技術(shù),2012,37(17):55-57.

[6] 蔣鵬,吳建峰,董林璽.一種改進(jìn)的無(wú)線(xiàn)多媒體傳感器網(wǎng)絡(luò)分布式圖像壓縮算法[J].傳感技術(shù)學(xué)報(bào),2012,25(6):815-820.

[7] 張健,吳曉冰.LVDS技術(shù)原理和設(shè)計(jì)簡(jiǎn)介[J].電子技術(shù)應(yīng)用,2000,26(5):59-61.