文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.015

中文引用格式: 唐學鋒. 低相位噪聲寬帶LC壓控振蕩器設計[J].電子技術應用,2015,41(11):54-57.

英文引用格式: Tang Xuefeng. Design of wide-band LC VCO with low phase noise[J].Application of Electronic Technique,2015,41(11):54-57.

0 引言

壓控振蕩器(Voltage-Controlled Oscillator,VCO)是鎖相環中的重要組成部分,能夠提供頻率準確、低相位噪聲的本振信號,它對鎖相環的性能甚至是整個射頻前端的性能都有著較大的影響。隨著無線通信網絡的快速發展,越來越多的射頻電路需要收發機能夠覆蓋很寬的頻率范圍,同時保持較低的相位噪聲性能,這無疑對壓控振蕩器的設計提出了更高的要求。

無線傳感網廣泛應用于交通、節能、環境保護、家庭網絡、生物醫療等領域。本文針對2.4 GHz頻段無線傳感網射頻收發機應用,采用0.13 μm CMOS工藝,設計了一個低相位噪聲寬帶LC壓控振蕩器。采用開關電容陣列把需要覆蓋的頻率調諧范圍分成若干個子頻段,從而降低了VCO調諧增益(Kvco),減小了相位噪聲。同時采用可變電容陣列來提高頻率調諧曲線的線性度,減小Kvco的變化,提高鎖相環的穩定性。本文設計的壓控振蕩器需覆蓋4.8 GHz~5.0 GHz 頻段, 輸出的差分信號將通過二分頻電路得到四路差分正交信號供收發機使用。考慮到工藝偏差、寄生等影響,設計的目標頻率范圍為4.6 GHz~5.3 GHz。

1 電路設計

1.1 電路結構

在目前廣泛應用的數模混合式鎖相環中,主流壓控振蕩器的實現主要有兩種結構:環形壓控振蕩器和LC壓控振蕩器。環形振蕩器能獲得大的調諧范圍,易于集成,但是其相位噪聲性能不理想,在無線通信應用中比較少。LC壓控振蕩器由于良好的噪聲性能已成功地應用在窄帶無線通信收發機中。近些年來一些寬帶的CMOS LC壓控振蕩器相繼報道出來[1-3],通過開關電容陣列和可變電容相組合,可以得到寬的調諧范圍并保持良好的相位噪聲性能。

本設計中,采用開關電容陣列和可變電容陣列相組合的電路結構,并同時采用NMOS管做負阻管。電路結構如圖1所示。L是片上集成電感,NMOS管M1、M2構成交叉耦合結構,提供振蕩所需的負阻。M3、M4構成電流鏡結構,為VCO提供偏置電流。

1.2 振蕩原理

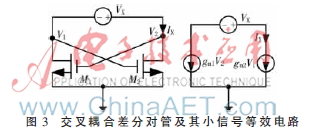

在LC 壓控振蕩器中,通常采用負電阻的概念來分析振蕩原理。一個理想電感L和電容C組成的并聯回路會在頻率ωres=1處諧振。實際上電感電容都存在寄生電阻,電阻會消耗回路的能量,使振蕩減弱最后停止。如果把一個與寄生電阻相等的負阻并聯在諧振電路,則振蕩回路會不停地振蕩下去。如圖2所示,RL表示由電感和電容引起的電阻損耗,RP表示由有源器件NMOS交叉耦合對提供的負阻。圖3是NMOS管交叉耦合對管及其小信號等效電路。忽略NMOS管的體效應和溝道長度調制效應, 可以得到[4-5]:

如果兩個NMOS管相同,即:gm1=gm2=gm,則:

當有源器件足以補償電阻損耗時,即:RL-2/gm≥0 時,LC壓控振蕩器能夠維持振蕩,此時gm≥2/RL。

在實際芯片制造和使用過程中, 由于存在溫度和工藝的變化,為了確保振蕩,在設計電路時,合理選擇M1、M2的尺寸及偏置電流使gm為所需值的兩到三倍,以保證在各種工藝角和溫度下都能起振。

1.3 電感元件

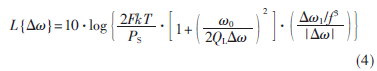

根據D.B.Lesson的相位噪聲模型[6]:

QL為諧振回路的品質因數,通過公式得知提高諧振回路的Q值可以降低相位噪聲。在目前的集成電路工藝中,片上電容的Q值要遠大于片上電感的Q 值,因此LC諧振回路的Q值主要由片上電感決定。要得到最小的相位噪聲,應該采用工作頻段內高Q 值的片上電感。

本設計采用工藝庫中的差分平面螺旋電感,如圖4所示。差分平面螺旋電感相對普通平面螺旋電感的優點是能夠利用差分電感內部的耦合,用小的面積實現大的電感值。除了可以節省版圖面積外,還具有更高的Q值以及提高版圖布局的對稱性。

1.4 開關電容陣列

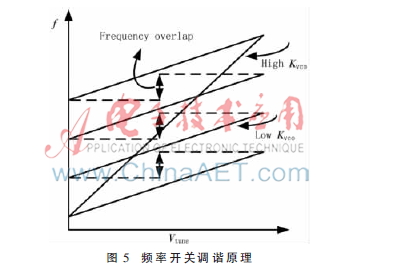

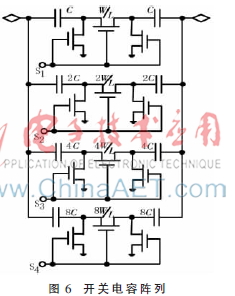

使用一個比值(Cmax/Cmin)大的MOS變容管能夠實現大的頻率調節范圍,但是此時,壓控振蕩器的調諧增益Kvco很大,大的Kvco會增大整個鎖相環系統的相位噪聲。本文采用開關電容陣列來將整個頻段劃分成若干個子頻段,如圖5所示。一條大范圍的頻率調諧曲線被分成4條小范圍的調諧曲線來實現,從而在保證頻率范圍不變的前提下減小了Kvco。相鄰兩條頻率曲線之間要有一定的交疊范圍,才能保證頻率調諧的連續性。本文采用4 bits控制開關,即16個子頻段。開關電容陣列如圖6所示,其中C是高品質因數的MIM電容,W/L是開關MOS管的寬長比,S4-S1是控制位。每路電容值和開關MOS管的寬長比設置為二進制加權形式。VCO的振蕩頻率可表示為:

Cfix為固定電容,Cvar為可變電容,通過開關控制位S4-S1來控制接入振蕩回路的固定電容值,從而得到多條調諧曲線。以一個控制單元為例,當控制位為高電平時,對應的固定電容接入振蕩回路,此時電容的品質因數為:

Ron為開關MOS管的導通電阻,

當控制位為低電平時,MOS管漏極寄生電容會影響調諧范圍。由式(7)、式(8)可知,要提高開關電容的Q值需要減小導通電阻Ron,也就是增大開關MOS管的寬長比(W/L)。但大的寬長比會增加MOS管關斷時的寄生電容,從而影響電路的諧振頻率,因此需要折中考慮[7]。

1.5 可變電容陣列

可變電容限制了VCO的頻率調諧范圍。本文所使用的0.13 μm RF CMOS工藝中提供積累型MOS管可變電容和PN結可變電容兩種結構。PN結可變電容的線性度高,但是品質因數低,可調范圍(Cmax/Cmin)小。本文采用N型積累型MOS管可變電容,其優點是品質因數Q值高,變容范圍也比較大,但是線性度比較差。

VCO頻率調諧(f-v)曲線的斜率即為調諧增益Kvco,得到:

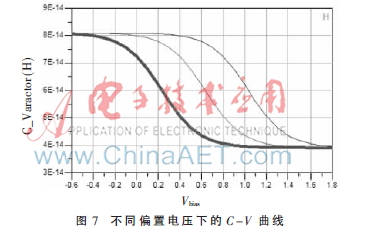

Cvar為可變電容值,可見要減小Kvco的變化就要提高變容管C-V曲線的線性度[5]。本文將對MOS變容管C-V曲線進行仿真并對其線性度優化。圖7是單個可變電容在三個不同偏置電壓下的C-V特性曲線,可見單條曲線的線性范圍比較小,這樣VCO不能完全利用0~1.2 V的調諧范圍。

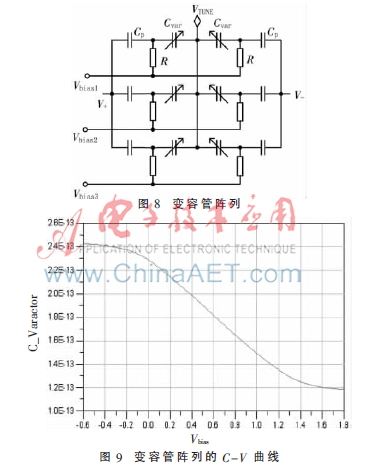

本文采用圖8所示的多偏置電壓變容管陣列來改善單個變容管的線性度。CP為隔直電容,R是偏置電阻。這種結構的效果是三個支路的C-V調諧曲線相疊加,合理選擇三個偏置電壓,可以增大C-V曲線的線性范圍,如圖9所示。在0~1.2 V的調諧電壓范圍內得到了較好的線性度,使得VCO的f-v曲線更加線性,Kvco變化更小,有利于鎖相環路穩定[8]。

2 仿真結果與分析

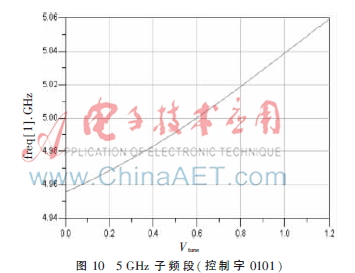

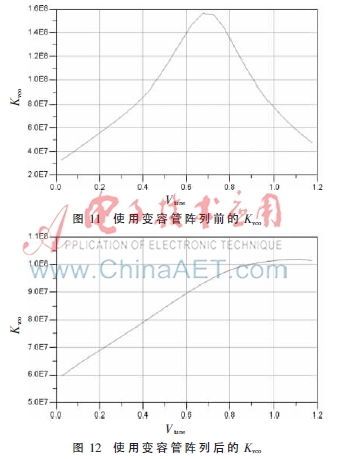

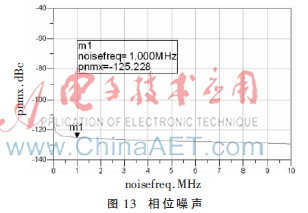

基于0.13 μm RF CMOS 1P6M工藝模型,使用安捷倫公司的射頻仿真軟件Advanced Design System(ADS)對電路進行優化仿真。圖10為中心頻率5 GHz所在子頻段(開關電容控制字為0101)VCO的f-v調諧曲線,可見采用變容管陣列結構后,在0~1.2 V調諧電壓范圍內實現了較好的線性度。圖11和圖12分別是使用變容管陣列前后對Kvco的仿真,用單個變容管時Kvco的變化范圍在30 MHz~156 MHz,在調諧電壓范圍內變化達5倍多,這會使鎖相環的環路帶寬變化很大,從而影響環路的穩定性。用變容管陣列結構后Kvco的變化范圍在60 MHz/V~102 MHz/V,大大減小了在調諧電壓范圍內的變化。圖13為本文所設計的VCO在中心頻率5 GHz處的相位噪聲仿真曲線,在1 MHz頻偏處為-125 dBc/Hz,滿足低相位噪聲設計的要求。

3 總結

采用0.13 μm RF CMOS工藝設計了一款頻率覆蓋范圍為4.58 GHz~5.35 GHz的寬帶壓控振蕩器。使用開關電容陣列有效地減小了調諧增益Kvco,降低了VCO的相位噪聲。采用可變電容陣列減小了Kvco的變化從而提高了鎖相環系統的穩定性。該VCO相位噪聲性能良好,可以應用到無線傳感網射頻前端。

參考文獻

[1] BERNY A D,NIKNEJAD A M,MEYER R G.A 1.8-GHz LC VCO with 1.3-GHz tuning range and digital amplitude calibration[J].IEEE J.Solid-State Circuits,2005,40(4).

[2] FONG N H W,PLOUCHART J O,et al,Design of wide-band CMOS VCO for multiband wireless LAN applications[J].J.Solid-State Circuits,2003,38(8).

[3] KIM J,SHIN J,et al,A wide-band CMOS LC VCO with linearized coarse tuning characteristics[J].Circuits and Systems II,2008,55(5).

[4] RAZAVI B.模擬CMOS基礎電路設計[M].陳貴燦,譯.西安:西安交通大學出版社,2003.

[5] 袁璐.寬帶電感電容壓控振蕩器的研究與設計[D].上海:復旦大學,2008.

[6] LEESON D B.A simplemodel of feedback oscillator noises spectrum[J].Proceedings of the IEEE,1996,54(2):329-330.

[7] KRAL A,BEHBAHANI F,ABIDI A A,RF-CMOS oscillators with switched tuning[C].IEEE Custom Integrated Circuits Conference,1998:555-558.

[8] MIRAI J,DIVELJ T.Distributed MOS varactor biasing forVCO gain equalization in 0.13 pm CMOS technology[J].IEEE Radio Frequency Integrated Circuits Symposium,2004:131-134.