1 概述

SoC 芯片設計的復雜度日益增加,其內部時鐘設計越來越復雜,一個SoC 芯片內部通常存在若干個時鐘域,由時鐘網絡引起的系統動態功耗成為近年來的研究熱點。時鐘網絡引起的系統動態功耗分為2 個方面:(1)由于時鐘網絡的作用是為芯片內部所有時序單元提供時鐘信號,因此時鐘頻率的快慢決定了時序單元和與之相連的邏輯單元的動態功耗,關斷時鐘將消除電路的動態功耗。(2)時鐘網絡自身的特點將導致巨大動態功耗的產生:1)時鐘網絡是芯片內規模最大的互連線網絡,其負載巨大,負載來自因為互連線電容和平衡時鐘樹的偏差而插入的大量延時單元;2)時鐘網絡是芯片內翻轉率最高的互連線網絡,翻轉率的高低直接決定了互連線動態功耗和互連線驅動的標準單元的動態功耗。

針對由時鐘網絡引起的2 種系統動態功耗,本文研究并實現3 種時鐘低功耗技術。

2 動態時鐘管理

一顆SoC 芯片的工作狀態變化很大,一些應用需要用到芯片內部的所有模塊,而另一些應用只要用到部分模塊;在某些應用中,芯片需要全速運行,而在其他應用中,則可以運行在很低的工作頻率[1]。綜合以上2 點,動態管理芯片的時鐘可以分為2 個方面:動態地開關芯片內部模塊的時鐘,動態地配置芯片內部模塊的時鐘頻率。

本文以音視頻解碼SoC 芯片——rsthu1 為例,介紹在系統級設計時采用的動態時鐘管理技術。

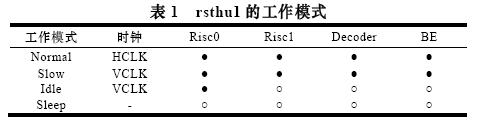

為了實現rsthu1 的動態時鐘管理,在芯片系統級設計時定義了4 種工作模式,見表1,其中,實心圓表示開啟此模塊;空心圓表示關閉此模塊。

當芯片工作在正常模式時,采用高速時鐘HCLK 供給Risc0, Risc1, Decoder, BE(Bit Engine)這4 個系統內的主要模塊,此時系統全速運行,進行音視頻解碼。當芯片工作在低速模式時,采用低速時鐘VCLK 供給上述4 個模塊,此時系統可以運行簡單的應用程序,保證了系統的持續工作,且降低了時鐘頻率,即降低了系統的動態功耗。當芯片工作在閑置模式時,只保留操作系統的運行,采用低速時鐘VCLK 供給Risc0,關斷其余模塊的時鐘供給,消除了除Risc0 以外其余模塊產生的動態功耗。當芯片工作在睡眠模式時,關斷所有模塊的時鐘供給,消除系統不工作時產生的動態功耗。

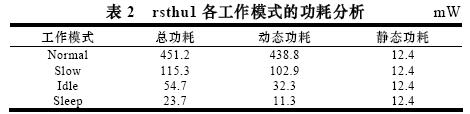

采用Synopsys 公司的功耗分析工具Prime Power,在RTL級基于4 種工作模式的仿真波形進行功耗分析,結果見表2。

可以看出,在系統級設計時采用動態時鐘管理技術后,正常、低速、閑置、睡眠4 個工作模式下,系統動態功耗逐級遞減,功耗優化效果明顯。

3 門控時鐘

RTL 代碼中經常會出現以下語句:

@posedge (CLK)

begin

if (EN == 1)

Data_out = Data_in;

end

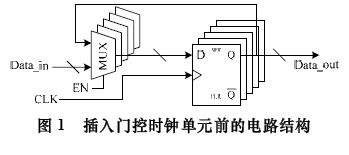

如果直接對上述代碼進行邏輯綜合將生成如圖1 所示的電路結構。控制寄存器狀態更新的控制信號被置于寄存器的輸入端之前,通過控制是否接收新數據來控制寄存器狀態是否更新。在該結構的電路中,寄存器狀態不更新時的寄存器時鐘端仍然在不停翻轉,會浪費系統動態功耗。

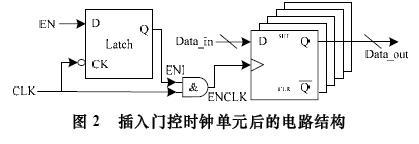

采用圖2 的結構,將控制信號置于寄存器的時鐘端之前,通過控制寄存器是否翻轉來控制寄存器狀態是否更新。與圖1 的電路結構相比,圖2 的電路結構在寄存器狀態不進行更新時,時鐘信號將不翻轉,消除了由此帶來的系統動態功耗的浪費。由于多個MUX 被替換為一個門控時鐘單元,因此進一步降低了功耗。

門控時鐘單元可以通過Synopsys 公司的功耗優化工具Power Compiler 在邏輯綜合時插入,其優點在于[3]:(1)不需要對RTL 級代碼進行修改,Power Compiler 將自動檢測出RTL 代碼中可以插入門控時鐘的語句;(2)門控時鐘單元將在邏輯綜合時自動插入門級網單中。

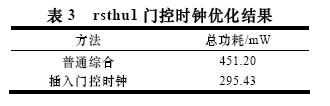

采用Power Compiler 對rsthu1 進行門控時鐘綜合,并采用Prime Power 進行功耗分析,結果如表3 所示。可以看出,在邏輯綜合時采用門控時鐘技術,總功耗下降了34.52%,功耗優化效果明顯。

4 低功耗時鐘樹綜合

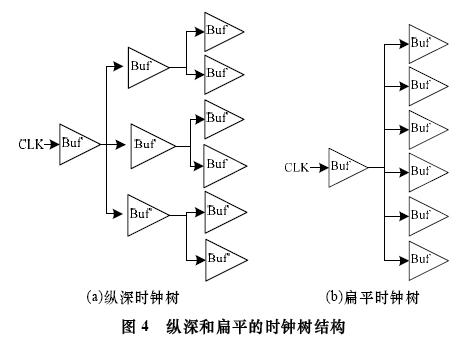

觀察時鐘樹的生長過程,可以發現時鐘樹的生長分為橫向擴張和縱向延伸,如圖3 所示,其中,Arrow1 和Arrow3為縱向延伸;Arrow2 為橫向擴張。

普通的時鐘樹綜合以降低時鐘偏差為目標,加大縱向延伸,減小橫向擴張,將投入較多buffer,更細粒度地調整每條時鐘路徑的延時,從而得到較小時鐘偏差。上述方式以增大時鐘樹規模為代價,它綜合得到的時鐘樹如圖4(a)所示。

出于功耗的考慮,希望能減小時鐘樹的規模。通過減小時鐘樹縱向延伸,加大橫向擴張可以有效減小時鐘樹的規模,如圖4(b)所示。但由于buffer 數量的減少,較之縱深結構的時鐘樹,扁平結構的時鐘樹將粗粒度地調整每條時鐘路徑的延時,得到的時鐘偏差較大。可見,以降低時鐘樹規模為目標,進行低功耗時鐘樹綜合是以增加一定的時鐘偏差為代價的。

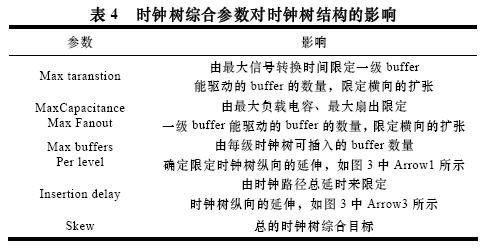

后端工具在進行時鐘樹綜合時,能通過綜合參數對時鐘樹結構進行約束,見表4。

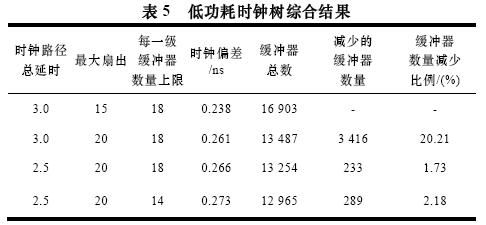

對rsthu1 的快速時鐘HCLK 進行時鐘樹綜合時,采用以降低時鐘樹規模為目標的低功耗時鐘樹綜合,結果如表5 所示。分別加大最大扇出,減小路徑總延時和每一級緩沖器數量上限。加大最大扇出后,時鐘樹規模減小了20.21%,而時鐘偏差只增加了0.023 ns,因此,由減小時鐘樹規模而帶來的偏差結果的變差是可以接受的。

5 結束語

目前已有很多時鐘低功耗技術,在SoC 芯片的設計中可以進一步降低由時鐘網絡引起的功耗。在以后的研究工作中,需要進行更廣泛而深入的探索。