1 引言

隨著數字信號處理" title="數字信號處理">數字信號處理越來越廣泛的應用,數字鎖相環DPLL(Digital Phase Lock Loop)在現代集成電路設計中也越來越普遍,特別是在數字信號處理器DSP 和微處理器這類高性能數字電路應用中,數字鎖相環更是一種必不可少的電路。與傳統的模擬鎖相環(Analog Phase-Locked Loop)相比,由于數字鎖相環較少采用高阻值電阻、電容以及電感等非線性器件,可以采用與高速數字邏輯電路相兼容的制造工藝來設計和制造,也更加容易在數字系統中應用。

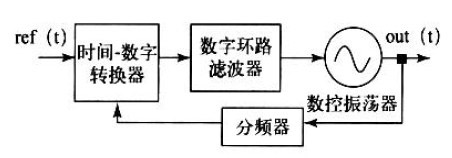

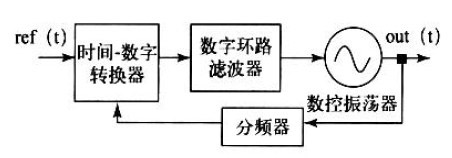

一個典型的數字鎖相環結構如圖1 所示,數控" title="數控">數控振蕩器" title="振蕩器">振蕩器DCO(Digital-Controlled Oscillator)是其中最關鍵和核心的部分。數控振蕩器DCO 輸出了可變頻率的振蕩波形,決定了整個鎖相環的噪聲性能和功耗。數字時間轉換器(Time - to - DigitalConverter)輸出了參考時鐘和反饋來的輸出時鐘之間的相位差,一個數字環形濾波器(Digital LoopFilter)代替了模擬環形濾波器來控制DCO,由與參考時鐘的相位差來控制DCO 輸出或高或低的振蕩頻率,輸出振蕩信號由負反饋送到數字時間轉換器,使相位差減小,最終讓輸出信號頻率與參考時鐘頻率一致,即達到相位鎖定。整個DCO 因此不再需要含有電容或電感,同時也減少漏電流和電源噪音的問題。

圖1 數字鎖相環的基本結構

2 電路結構和原理

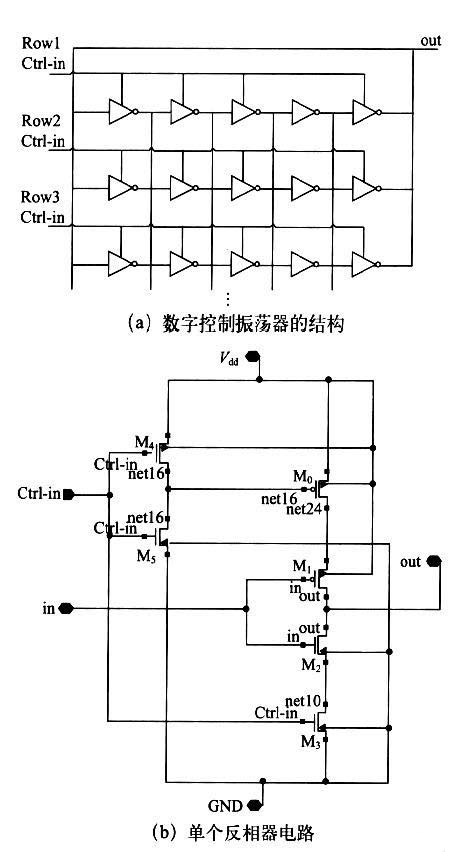

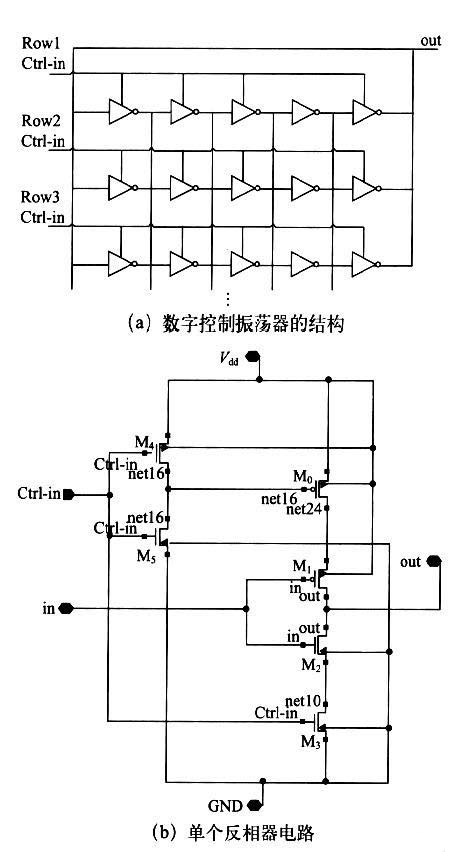

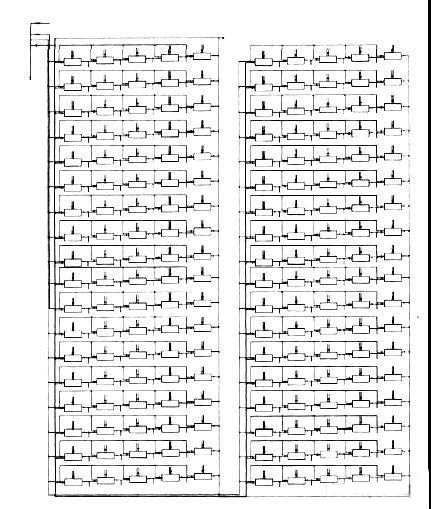

數控振蕩器有多種實現結構,本文設計了一種完全采用靜態CMOS" title="CMOS">CMOS 邏輯電路的DCO結構,該DCO基于由CMOS 反相器構成的環形振蕩器,其電路結構如圖2 所示。

圖2 電路結構圖

如圖2 所示,每一級環形振蕩器均是5 個CMOS反相器串聯,并構成閉環負反饋回路,每個反相器的輸出也與下一級環形振蕩器對應的反相器輸出相連。根據巴克豪森準則:振蕩器要產生振蕩,那么環路增益必須大于等于一且總相移有360°。因此環路中進行反相的次數必須是奇數,三個以上的奇數個CMOS 反相器串聯閉環回路,在一個微小的激勵下都能夠產生振蕩。單級環形振蕩器的振蕩頻率由反相器個數和其本征延遲決定,用n 表示反相器個數,tr 表示反相器上升沿延遲,tf 表示反相器下降沿延遲,頻率可以用下式表示為:

反相器下降延遲t f 和上升延遲t r 根據下列公式定義,式中Rn、Rp 分別為圖2(b)中反相器PMOS管M0、M1 和NMOS 管M2、M3 的等效電阻,Cout 為反相器輸出電容。

設置電路中所有MOSFET的溝道長度都為90nm工藝設計規范的默認值0.1 μ m。因為在常溫下N 溝道中的電子遷移率大約是P 溝道中的空穴遷移率的2~3 倍,因此設置PMOS 管的寬度Wp 是NMOS 管寬度Wn 的2 倍,使反相器中NMOS 管和PMOS 管的等效電阻近似相等,即Rn=Rp,也就使tr=tf。

下降延遲t r 和上升延遲t f 相等可以讓環形振蕩器產生對稱性比較好的波形,提高振蕩器的抗噪聲性能。

1 引言

隨著數字信號處理越來越廣泛的應用,數字鎖相環DPLL(Digital Phase Lock Loop)在現代集成電路設計中也越來越普遍,特別是在數字信號處理器DSP 和微處理器這類高性能數字電路應用中,數字鎖相環更是一種必不可少的電路。與傳統的模擬鎖相環(Analog Phase-Locked Loop)相比,由于數字鎖相環較少采用高阻值電阻、電容以及電感等非線性器件,可以采用與高速數字邏輯電路相兼容的制造工藝來設計和制造,也更加容易在數字系統中應用。

一個典型的數字鎖相環結構如圖1 所示,數控振蕩器DCO(Digital-Controlled Oscillator)是其中最關鍵和核心的部分。數控振蕩器DCO 輸出了可變頻率的振蕩波形,決定了整個鎖相環的噪聲性能和功耗。數字時間轉換器(Time - to - DigitalConverter)輸出了參考時鐘和反饋來的輸出時鐘之間的相位差,一個數字環形濾波器(Digital LoopFilter)代替了模擬環形濾波器來控制DCO,由與參考時鐘的相位差來控制DCO 輸出或高或低的振蕩頻率,輸出振蕩信號由負反饋送到數字時間轉換器,使相位差減小,最終讓輸出信號頻率與參考時鐘頻率一致,即達到相位鎖定。整個DCO 因此不再需要含有電容或電感,同時也減少漏電流和電源噪音的問題。

圖1 數字鎖相環的基本結構

2 電路結構和原理

數控振蕩器有多種實現結構,本文設計了一種完全采用靜態CMOS 邏輯電路的DCO結構,該DCO基于由CMOS 反相器構成的環形振蕩器,其電路結構如圖2 所示。

圖2 電路結構圖

如圖2 所示,每一級環形振蕩器均是5 個CMOS反相器串聯,并構成閉環負反饋回路,每個反相器的輸出也與下一級環形振蕩器對應的反相器輸出相連。根據巴克豪森準則:振蕩器要產生振蕩,那么環路增益必須大于等于一且總相移有360°。因此環路中進行反相的次數必須是奇數,三個以上的奇數個CMOS 反相器串聯閉環回路,在一個微小的激勵下都能夠產生振蕩。單級環形振蕩器的振蕩頻率由反相器個數和其本征延遲決定,用n 表示反相器個數,tr 表示反相器上升沿延遲,tf 表示反相器下降沿延遲,頻率可以用下式表示為:

反相器下降延遲t f 和上升延遲t r 根據下列公式定義,式中Rn、Rp 分別為圖2(b)中反相器PMOS管M0、M1 和NMOS 管M2、M3 的等效電阻,Cout 為反相器輸出電容。

設置電路中所有MOSFET的溝道長度都為90nm工藝設計規范的默認值0.1 μ m。因為在常溫下N 溝道中的電子遷移率大約是P 溝道中的空穴遷移率的2~3 倍,因此設置PMOS 管的寬度Wp 是NMOS 管寬度Wn 的2 倍,使反相器中NMOS 管和PMOS 管的等效電阻近似相等,即Rn=Rp,也就使tr=tf。

下降延遲t r 和上升延遲t f 相等可以讓環形振蕩器產生對稱性比較好的波形,提高振蕩器的抗噪聲性能。

每一級的5 個CMOS 反相器由一個高電平有效的輸入信號控制,同時打開或者關閉,讓DCO 中的環形振蕩器逐級打開或者逐級關閉。當打開的環形振蕩器級數越多,電路中的振蕩電流越強,電路輸出的振蕩頻率就越快。反之,當打開的環形振蕩器級數越少,電路中的振蕩電流減弱,但因為整個DCO中的環形振蕩器總級數是一定的,因此整個DCO 中的等效電容并沒有減少,所以輸出的振蕩頻率就會下降。因此,該數控振蕩器是通過控制打開的環形振蕩器級數,數字化地控制振蕩頻率,在DPLL中需要一個前置的數字環形濾波器提供輸入信號,控制各級振蕩器的打開或關閉。

當所有環形振蕩器都打開時,無論該DCO 中總共有多少級環形振蕩器,DCO 輸出的振蕩波形的最大頻率fmax 都為式(1)表示的單個環形振蕩器振蕩頻率。輸出的最小頻率fmin 也就是當只有一級環形振蕩器打開時的DCO 輸出頻率。由此分析,DCO 的增益可以如下式表示,式中N 為電路中總的環形振蕩器級數:

由上述分析可見,當該DCO 中具有的總的環形振蕩器級數越多,可以輸出的fmin 越小,KDCO 也越小,也就是每一級環形振蕩器開關所控制的頻率增減也越小,振蕩器線性度也就越好。

3 仿真結果

本文基于STMicroelectronics的90nm CMOS混合信號工藝,采用Cadence Virtuoso 設計軟件,使用Analog Environment 中的Spectre仿真器進行仿真。由于電路完全與數字集成電路工藝兼容,因此也可以采用諸如硬件描述語言來設計電路。

由32 級環形振蕩器構成的數控振蕩器DCO 在Cadence Virtuoso 中的仿真電路如圖3 所示,在本文的仿真中,是使用直流電壓作為控制DCO 各級環形振蕩器打開或者關閉的輸入信號。

圖3 32級的DCO結構仿真電路圖

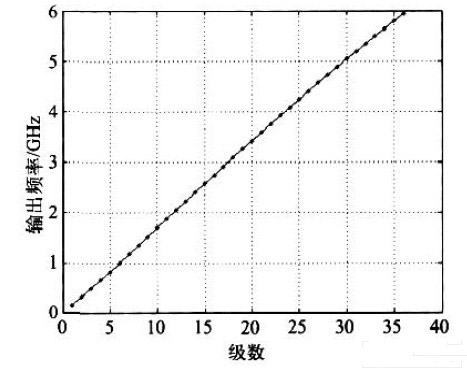

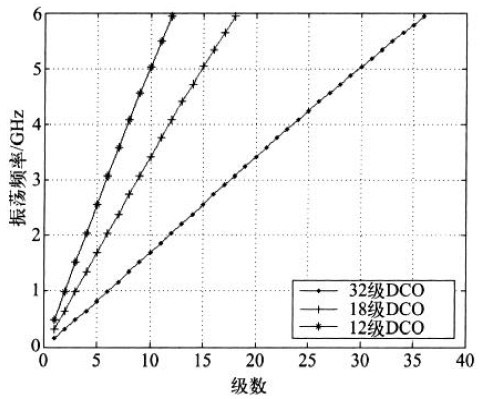

電路中電源電壓VDD=1.2V,所有MOSFET 均采用9 0 n m 工藝庫中的標準電壓晶體管S V T(Standard Vol tage Tr ansi st or ),其閾值電壓為Vthn=0.3V,|Vthp|=0.3V。當32級環形振蕩器逐級打開,數控振蕩器輸出波形的振蕩頻率也逐級上升,整個數控振蕩器的頻率調節范圍如圖4 所示。

圖4 DCO輸出頻率調節曲線

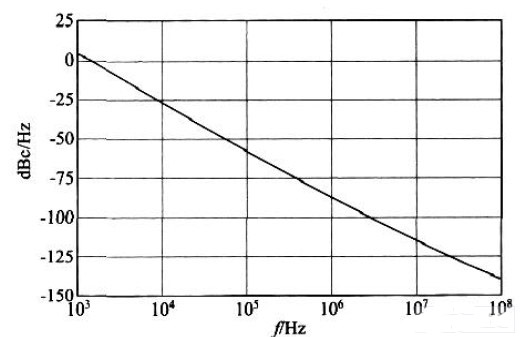

當32 級DCO中的18 級環形振蕩器打開的時候,DCO 的相位噪聲如圖5 所示。相位噪聲由Spectre 仿真器的pss 分析和pnoi se 分析測得。

圖5 打開18 級時的DCO相位噪聲

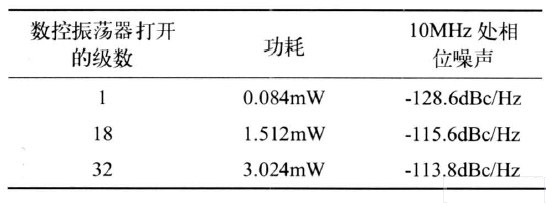

該32 級數控振蕩器的相位噪聲和功耗如表1 所示,隨著環形振蕩器逐級打開,相位噪聲和功耗都明顯上升,這是獲得高頻率輸出波形所付出的性能代價。先測得單個反相器的平均電流,測得各個打開的反相器平均電流均約為14 μ A,由下式可以得到電路的總功耗,式中N 為打開的環形振蕩器級數。

為了研究環形振蕩器級數對頻率調節范圍的影響,將數控振蕩器的級數減少至18 級或12 級,再分別測試其頻率調節范圍。三種不同級數數控振蕩器調節范圍的對比如圖6 所示,不同級數的數控振蕩器fmax 相等,但fmin 隨著數控振蕩器的總級數增加而減小,且KDCO 也變小,調節線性度更好。

圖6 不同級數數控振蕩器的頻率調節范圍

表1 數控振蕩器不同級打開時的相位噪聲和功耗

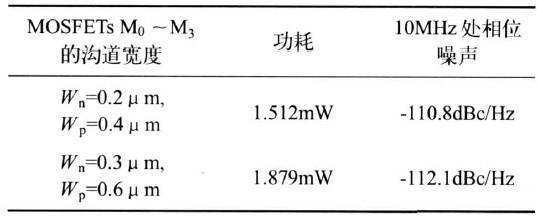

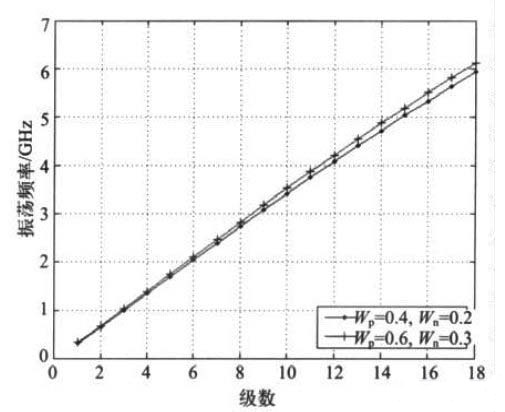

進一步測試器件尺寸對數控振蕩器性能的影響,當器件寬度Wn 和Wp 增加,反相器中的平均電流增加,可以輸出更高的頻率并減小電路中器件噪聲導致的相位噪聲,這對高性能電路是有意義的,但電路功耗也隨之增加。對于18 級數控振蕩器,保持電路中全部MOSFET 的溝道長度不變,同時增大圖2(b)中的NMOS 管M2、M3 的Wn和PMOS 管M0、M1 的Wp至原尺寸的1.5 倍后測得的頻率調節范圍如圖7 所示,全部環形振蕩器共18 級打開后的DCO 功耗 及相位噪聲如表2 所示。

表2 器件尺寸不同時測得的功耗及相位噪聲

圖7 器件尺寸不同時測得的頻率調節范圍對比

4 結論

該數控振蕩器結構采用全靜態CMOS 邏輯電路來設計,獲得了線性度較好的頻率調節范圍,在90nm混合信號工藝條件下全DCO電路功耗在3mV左右,10MHz處相位噪聲低于-110 dBc/Hz,性能相比傳統LC 壓控振蕩器有過之而無不及,非常適合應用于高性能數字電路中。在用該數控振蕩器結構設計DPLL 時,應進一步增加環形振蕩器級數以提供線性度更好的可調輸出頻率范圍,并需要前置數字環形濾波器提供相配合的控制信號。