摘? 要: 幀存是圖形顯示系統" title="顯示系統">顯示系統的核心部件之一,幀存的設計關系到系統的整體性能。介紹了一種高速圖形幀存的設計方法。該高速幀存采用SRAM作為存儲體,應用FPGA實現雙幀存交替切換、上電" title="上電">上電清屏等功能,并借鑒電影遮光板的原理實現單幀雙掃描功能,增加了系統視頻帶寬。該幀存已在某型飛機座艙圖形顯示系統中獲得成功應用。

關鍵詞: 圖形幀存? 儀表裝置? LCD ?VHDL? FPGA

?

幀存是圖形處理器與顯示設備之間的數據通道,所有要顯示的圖形數據首先是存放在幀存之中,然后才送出去顯示的,因此幀存的設計是圖形顯示系統設計的一個關鍵。傳統上,可以用來設計幀存的存儲器件有多種,如DRAM、VRAM、SDRAM及SRAM等。DRAM、VRAM及SDRAM屬于動態存儲器,容量大、價格便宜,但速度比SRAM慢,而且在使用中需要定時刷新。當圖形處理器沒有外部專用刷新接口時,就需要設計刷新電路,這給系統設計帶來不便。SRAM器件高速且接口簡單,但是價格較貴、容量小。近年來,隨著SRAM容量的不斷增大和價格的不斷下降,在一些需要高速實時顯示的圖形顯示系統中,用高速SRAM設計圖形幀存越來越普遍。本文介紹已在項目中實際應用的采用雙SRAM幀存交替切換的高速幀存設計方法。詳細介紹應用FPGA設計幀存控制器,實現幀存的交替、上電清屏及借鑒電影遮光板原理實現單幀雙掃描的方法。

1 圖形顯示系統簡介

圖1是某專用圖形顯示系統結構框圖,圖形顯示系統采用DSP+FPGA構架。圖形處理器采用AD公司的ADSP21061芯片;AMLCD采用Korry公司的KDM710全彩色液晶顯示模塊,該模塊為5×5英寸、600×600分辨率全彩色液晶顯示模塊,24位數字RGB輸入;兩個幀存A和B采用IDT公司的71V424L10Y高速異步靜態RAM(讀寫速度為10ns)。系統采用雙幀存輪流操作方法:當DSP向其中一個幀存寫像素時,由FPGA構成的幀存控制器將另一個幀存中的像素順序讀出,送給AMLCD顯示;反之亦然。圖形顯示系統通過IDT公司的71V04雙口RAM接收主機的顯示信息。圖1中的幀存控制器和視頻控制器由Xilinx公司的SpartanII芯片XC2S50實現。 視頻控制器產生KDM710顯示模塊所需的一些時序控制信號:行同步信號" title="同步信號">同步信號/HSYNC、場同步信號/VSYNC、數據使能信號DATA_EN和像素時鐘信號DCLK等。幀存控制器產生24位RGB顏色數據信號,該RGB數據信號與視頻控制器中的時序控制信號相配合,在液晶顯示屏上顯示出穩定的圖形。有關視頻控制器的設計方法參見文獻[2]。

?

?

2 幀存控制器設計

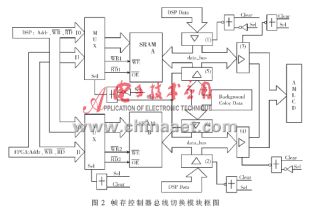

2.1 總線切換模塊

圖2為幀存控制器總線切換模塊框圖。地址總線" title="地址總線">地址總線通過多路選擇器(MUX)切換,所有數據總線通過三態門掛在SRAM的數據總線上。幀存SRAM的數據總線上掛著三路數據:一路是DSP的數據總線數據;一路是FPGA的數據總線數據;還有一路是系統上電清屏用的背景寄存器數據(系統剛上電時,幀存之中存放的是隨機數,畫面顯示的將是隨機畫面,需要將背景數據送入兩個幀存)。總線的切換由體切換信號Sel和上電清屏信號Clear控制。幀存控制器在上電時,通過上電清屏時序將兩塊幀存中寫入背景顏色數據。在上電清屏過程中,Clear信號為高。當Clear為高時,兩個地址總線選擇器都選擇FPGA總線,即FPGA的地址總線指向兩個幀存,兩個幀存的數據總線全指向背景數據寄存器,即三態門1、2、3和4關閉,而三態門5和6打開。在上電清屏時序完成之后,幀存總線的控制由體選擇信號Sel控制。當DSP對幀存A進行寫操作時,FPGA所產生的總線對幀存B進行讀操作;反之亦然。如圖2所示,當Sel為高時,DSP地址總線選擇幀存A,三態門1打開,三態門3、5關閉;FPGA地址總線選擇幀存B,相應的數據總線三態門4打開,2、6關閉。背景寄存器中的顏色數據可以由用戶自己定義。

?

?

2.2 控制模塊

幀存控制器的控制模塊" title="控制模塊">控制模塊產生體選擇信號Sel和上電清屏時序信號Clear,控制模塊的結構框圖如圖3所示。圖中,/VSYNC是場同步信號,該信號經過一個微分電路,產生一個像素時鐘周期寬的使能脈沖信號,控制計數器的計數使能。計數器為一模2計數器,Sel信號為場同步信號/VSYNC的四分頻,在出現兩個場同步信號之后,才切換幀存,即兩個幀存使用的順序是:AABBAA...這種控制方式類似于電影遮光板的設計思想,使一幅畫面在屏幕上重復出現兩次,從而在25Hz的幀頻時能獲得50Hz的場頻,使系統視頻帶寬增加一倍。如當場頻50Hz時,圖形處理器可以有40ms的時間處理一幀圖形數據。圖4為幀存控制時序圖,Clear信號的產生過程如下:系統上電時,RST信號高一段時間(系統邏輯復位)后變低,在RST的下降沿,ClearA變高,此時場同步低電平有效信號還沒到,ClearB為高,Clear為高,系統開始清屏時序。當對兩個幀存的清屏工作結束時,場同步信號/VSYNC有效,該信號將“0”電平鎖存輸出,ClearB為低,Clear為低,系統開始在Sel控制下工作。從控制模塊框圖中可以看到,Clear信號僅僅在上電復位信號RST結束時(下降沿)才變為高,持續一個場周期之后,Clear信號將一直為低,把控制權交給Sel體切換信號。控制模塊的VHDL代碼及相應的時序仿真圖如圖5所示(Modelsim5.5FSE仿真器仿真)。

?

?

entity sel_gen is

port(clk ??????? : ?? in std_logic;

???? rst?????????? :??? in std_logic;

???? vsync???????? :??? in std_logic;

???? sel?????????? :??? out std_logic;

???? clear?????????:??? out std_logic);

end sel_gen

architecture rtl_sel_gen of sel_gen is

signal clken?????????:?? std_logic;

signal cleartemp???? :?? std_logic;

signal inputrega???? :?? std_logic;

signal inputregb???? :?? std_logic;

signal qn??????????? : ? std_logic_vector(1 downto 0);

signal seltemp?? ?? : ? std_logic;

begin

process(rst,vsync)

begin

if rst'event and rst=‘0’ then

cleartemp <=‘1’;

end if;

if(vsync=‘0’)then

cleartemp <=‘0’;

end if;

end process;

clear<=cleartemp;

process(clk)

begin

if clk'event and clk=‘1’then

inputregb <= inputrega;

inputrega <= not vsync;

end if;

end process;

clken <= not inputregb and inputrega;

process (clk,rst)

begin

if (rst-‘1’) then

qn <= (others = >‘0’);

elsif clk'event and clk = ‘1’ then

if clken=‘1’ then

if qn = 3 then

qn <= (others =>‘0’);

else

qn <=qn +1;

end if;

end if;

end if;

seltemp <=qn(1);

end process;

sel <= seltemp;

end rtl sel gen;

?

3 時序分析

要使高速幀存能正常工作,必須滿足一定的時延要求。AMLCD是在像素時鐘的下降沿將數據鎖存,從像素時鐘的上升沿到正確的RGB圖形數據出現在AMLCD的數據總線上,之間的延時T必須小于25ns(像素時鐘周期為50ns,半周期為25ns),系統才能正常工作,如圖6所示。圖中的DLL(Delay-Locked Loop)為SpartanII芯片內置的數字鎖相環,Clk_top(40MHz)經DLL二分頻后得20MHz像素時鐘。20MHz時鐘一路作為系統工作時鐘為FPGA地址計數器提供計數脈沖,一路作為像素時鐘直接送至AMLCD。從圖6可以看出,延時T包括如下幾個延時:T1為Clk_top到幀存SRAM地址總線上地址的改變所需的延時(總線上各個信號的延時是不同的,T1為其中最大值);T2為幀存SRAM從地址改變到有效的數據出現在數據總線上所需的延時;T3為FPGA讀幀存數據總線上的數據到輸出至AMLCD所需的延時;T4為Clk_top經DLL產生像素時鐘直接輸出至AMLCD所需的延時。可以看出延時T=T1+T2+T3-T4。系統中的幀存控制器由Xilinx公司的SparatnII 芯片XC2S50-6實現,經過FPGA Express3.7綜合和Xilinx公司的ISE4.2I軟件布局布線。經分析,布線后的延時:T1=10.994ns、T3=10.691ns、T4=7.784ns,T2 由IS61LV5128芯片的時間參數決定,T2≤10ns,從而T≤23.901ns<25ns,滿足系統的時序要求。一般開發工具所得出的時序報告是系統最壞情況下的延時,實際系統中的延時將小于仿真時所得出的數據。

?

?

采用高速SRAM存儲器作為圖形幀存,用FPGA設計幀存控制器,能大大減小電路板的尺寸,增加系統的可靠性和設計靈活性;采用雙幀存交替切換及單幀雙掃技術,提高了系統視頻帶寬,并能提高系統實時性,減少圖形閃爍;采用VHDL語言進行FPGA設計具有方法簡單、易讀和可重用性強的特點。該高速圖形幀存已用Xilinx公司的SpartanII系列器件XC2S50實現,并在某型飛機座艙圖形顯示系統中實際應用。

?

參考文獻

1 The programmable Logic Data Book 2000. USA:Xilinx?Corp,2000

2 朱耀東.基于FPGA的LCD&VGA控制器設計.電子技術應用, 2002;28(11)

3 蘇光大. 微機圖象處理系統. 北京:清華大學出版社2000.7: 65~92

4 KDM710 5X5 AMLCD-Interface control document. USA:?Korry Electronics Corp,2001.6