子系統劃分選擇方案

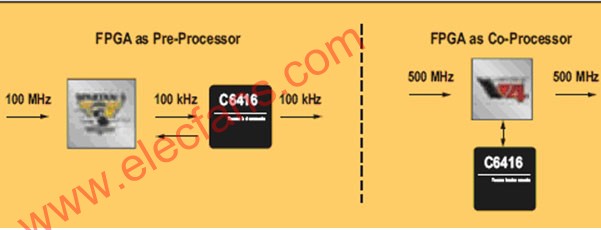

FPGA可與DSP處理器一起使用,作為獨立的預處理器(有時是后處理器)器件,或者作為協處理器。在預處理架構中,FPGA直接位于數據通路中負責信號預處理,預處理后的信號可以高效又經濟地移交給DSP處理器進行速率較低的后續處理。

在協處理架構中,FPGA與DSP并列而置,后者將特定算法函數卸載給FPGA,以便實現比單獨采用DSP處理器能達到的速度更高的處理速度。FPGA的處理結果傳回DSP,或者送至其他器件進一步進行處理、傳輸或存儲(圖1)。

選擇預處理、后處理還是協處理,常常取決于在處理器和FPGA之間移動數據所需的時序余量及其對整體延遲的影響。雖然協處理解決方案是設計人員最常考慮的拓撲結構(主要是因為DSP可以更直接地控制數據移交過程),但這并不一定總是最佳的總體策略。

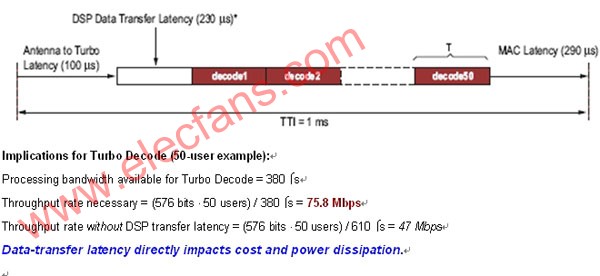

例如,最新的3G LTE規范將傳輸時間間隔(TTI)從HSDPA的2ms和WCDMA的10ms縮短到了1ms。這實質上是要求從接收器一直到MAC層輸出之間的數據處理時間短于1,000?sec。

圖1:FPGA 用作預處理器和協處理器的解決方案

如圖2所示,在運行速度為3.125Gbps的DSP上使用SRIO端口(使用8b/10b編碼,Turbo解碼功能需要200比特的額外開銷)會造成230?sec的DSP到FPGA傳輸延遲(也就是說TTI時段中有將近四分之一僅用來傳輸數據)。加之其他可預見的延遲,為滿足這些系統時序,當用戶為50個時,所需的Turbo編解碼器性能就是高達75.8Mbps。

圖2:協處理數據傳輸延遲問題的 LTE 示例

使用FPGA將Turbo編解碼器作為基本上獨立的后處理器來處理,不僅可消除DSP延遲,還能節省時間,因為不需要以高帶寬在DSP和FPGA之間傳輸數據。這樣做可將Turbo解碼器的吞吐量降至47Mbps,因而可選用更多比較經濟的器件,并且可以減少系統功耗。

另一項考慮是在XilinxFPGA上是否使用軟嵌入式或硬嵌入式處理器IP來卸載某些系統處理任務,進而可能進一步減少成本、功耗和占用空間。有了如此大量的信號處理資源,就可以在DSP處理器、FPGA可配置邏輯塊(CLB)、嵌入式FPGA DSP模塊和FPGA嵌入式處理器之間更好地分配各種復雜功能(如基帶處理中的復雜功能)。Xilinx提供了兩種類型的嵌入式處理器:MicroBlaze軟核處理器(常用于系統控制)和性能更高的PowerPC硬核嵌入式處理器(用于更復雜的任務)。

FPGA嵌入式處理器提供的有利條件允許將所有非關鍵性操作都合并到在嵌入式處理器上運行的軟件中,從而盡量減少整體系統所需的硬件資源總量。

軟件和IP的重要性

關鍵問題是如何將這種潛在能力全部釋放出來。必須考慮需要用哪些軟件對問題的復雜性進行抽象以及可以使用哪些IP,應該考慮利用FPGA為關鍵部分提供最佳解決方案。

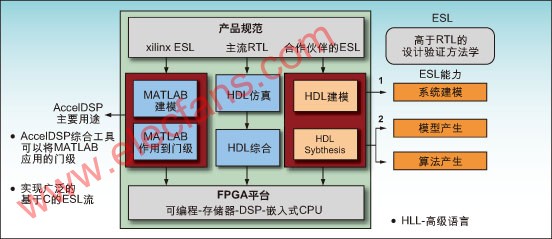

Xilinx致力于開發行業領先的工具和體系,能夠在比HDL工具(如MATLAB模型和C代碼)所能提供的更高的抽象層上實現高效的FPGA解決方案。利用Xilinx專門用于DSP的系統生成開發工具和AccelDSP綜合工具,可以盡可能無縫實現從算法到硅片的鏈接。

目前有一個日益重要的工具提供商團隊,其產品通過C/C++到邏輯門的設計流程把開發提升到電子系統級(ESL)。ESL設計工具的目的是提供一種完備的系統級方法,以便生成和集成硬件加速功能以及控制這些功能的處理器的控制代碼。

沒有哪一種高級語言或軟件工具能適合當今復雜系統中所見的所有不同單元。語言和設計流程的選擇取決于客戶,有時取決于具體的工程師。因此,Xilinx開發了一套齊全的集成功能,以滿足客戶需求并提供最佳設計環境(見圖3)。

圖3:系統級到 FPGA 設計流程

本文小結

另外,Xilinx正在斥巨資提供一套功能廣泛的高價值IP、電路板和參考設計,以涵蓋射頻卡和基帶應用中的許多關鍵部分,其中包括FFT/iFFT、調制、數字上下變頻和波峰系數的降低電路等。

這一重點舉措的一個例子是開發針對特定無線標準和FPGA架構優化的行業領先的高性能FEC功能,如Turbo編碼器和解碼器。正如我們在分析3GLTE延遲和Turbo解碼器流量要求時所示,FEC功能的硬件加速及其對系統架構的作用在現代無線設備設計中是日漸緊要的當務之需。

雖然一些專家級DSP處理器陸續以嵌入式模塊的形式集成這類功能,但是,從制訂出符合新無線標準的FEC功能參數到形成嵌入式加速模塊出現在硅片中,通常需要好幾個月。一旦實現了嵌入,也還會有遺留的難題,偶爾還會有嵌入式模塊中的功能并非都能按要求工作的局面出現。同時,標準演化迅速,現標準中不時納入一些固定嵌入式模塊不能支持的新要求。