隨著摩爾定律的持續推進,AI和自動駕駛等應用的出現,芯片行業正迎來前所未有的新挑戰。

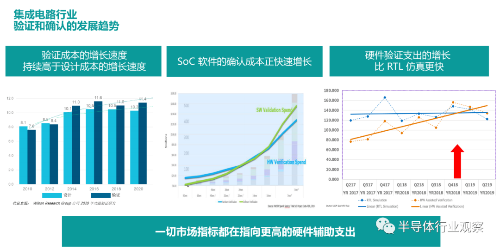

以芯片的驗證為例,Siemens EDA(之前的Mentor Graphic)全球副總裁兼中國區總經理凌琳在日前的一個媒體會上強調:“在當前整個半導體、集成電路行業當中,設計的驗證變得越來越重要”。據他所說,這可以從三個方面體現出來:首先,如下圖左所示,在過去的十年當中,驗證在芯片設計中的成本占比和發展是越來越快,它的增長速度是遠高于設計成本的增長速度。

“在整個前端的設計當中,包括工程師、軟件、硬件在內的驗證資源占到總成本的70%,而設計成本只占30%,這說明驗證在整個工作當中的占比會越來越高”,凌琳補充說。

其次,如上圖中所示,從不同的技術節點、硬件的驗證速度和軟件確認速度的發展比例來看,SoC軟件確認的成本正在快速增長。這主要因為任何一個SoC都是在一個更大的子系統或者更復雜的系統當中。那就意味著除了硬件本身的功能,還有很多效能、電源等都需要用操作系統或更多軟件去協同驗證,這是非常有難度的,它的需求量也增長得非常之快。

“最后,如上圖右所示,傳統仿真已經無法滿足我們對仿真時間效益的需求。而硬件加速平臺是一個快速的、新的發展趨勢,這也證明了整個驗證和確認的發展趨勢為什么會那么快。”凌琳表示。

在凌琳看來,現在SoC、IC的發展速度非常之快,不管是5G、通信、超算、存儲、云計算中心,還是運輸、交通工具、智能汽車、自動駕駛等領域,所有這些不同的應用領域對于SoC本身的設計和對功能的驗證仿真,包括將來進入哪些子系統或更復雜系統的認證、驗證方向和功效要求將會變得更為復雜。

“這種復雜不是線性增長,而是指數級增長,所以這就需要EDA廠商能夠開發出更易用、更方便的平臺和工具,來幫助他們完成這些非常艱難的技術演進和復雜度非常高的芯片和子系統的驗證及確認。只有具備這些技術,才能保證他們的芯片上市之后真正會有市場且是可量產的。對于SoC廠商或做芯片的公司來說,這些技術是他們的命脈。”凌琳強調。

Siemens EDA亞太區技術總監李立基則在媒體會上告訴記者,對于現在的芯片公司而言,他們做產品的過程中不但要考慮功能問題,還要考慮其性能問題。

“現在在市場上,我們要確定一個芯片是否成功,就是要看它跑軟件的性能,這跟以前只看它有多少不同功能截然不同。所以我們現在設計芯片的時候,需要將該軟件的工作負載直接跑到芯片上面去收集數據,做性能和功耗的分析,然后進行優化。所以在設計流程里我們要更早進行驗證,且在驗證的過程里面不只是做功能的驗證,也需要做性能、功耗方面的優化和支持。”李立基接著說。

正是在這些需求的推動下,Siemens EDA帶來了公司全新一代的 Veloce?全面硬件輔助驗證系統。據介紹,Veloce 硬件輔助驗證系統中的新產品包括用于虛擬平臺/軟件激活驗證的 Veloce HYCON、硬件仿真器Veloce Strato+、企業級 FPGA 原型驗證系統Veloce Primo和桌面 FPGA 原型驗證系統Veloce proFPGA。

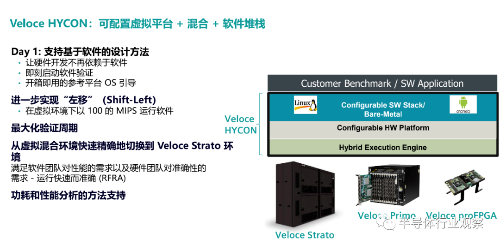

首先看Veloce HYCON(Hybrid Configurable的縮寫)。這是一個支持“左移”設計的平臺,也就是說開發者可以借助這個平臺顛覆傳統做好硬件,再做軟件測試的流程,及早地將其軟件跑在芯片上。這一方面減少了開發時間;另一方面則可以更早地將漏洞展現出來,方便開發者優化。

“Veloce HYCON包含了一個軟件的工具,作為一個虛擬的模型,它還有操作系統軟件。所以如果你是做一個系統,做一個產品,里面有Arm CPU,然后要跑到linux或安卓等操作系統上時,這個部分可以不需要放一個RTL進去,只是把你自己設計部分的硬件連到Veloce HYCON的模型上面,就可以去跑系統。”李立基告訴記者。

硬件仿真器Veloce Strato+則是Veloce 系統的另一重要組成部分。這也是Siemens EDA前一代產品Veloce Strato的升級。

據了解,公司上一代的Strato,一個機箱的容量是25億門,可以同時把四臺機箱串聯起來,所以Strato整體最大的容量是100億門。而對于現在的Strato+,把四臺機器連起來則能達到150億門容量,與比前一代的Veloce Strato增加了1.5倍。

“我相信這是目前行業里面容量最大的硬件仿真器。同時我們的功耗也有所降低。”李立基強調。在他看來,公司之所以能在Veloce Strato+創造這樣的成績,與公司自己研發的新芯片有很大的關系。

李立基在會上指出,公司在之前版本的Strato里面用的芯片是Crystal 3,如今全新的產品則用上了新芯片Crystal 3+。據了解,整個芯片的升級主要體現在存儲上。與前一代芯片的存儲是放在芯片外面的,然后在線路板上面把它連起來不一樣,Crystal 3+是用了最先進的2.5D的技術,將存儲都被放到封裝里面。通過這樣的設計,可以獲得更低功耗、更快速度和更小芯片面積。

“以前在同一個線路板上面可以放16個芯片,現在最多可以放24個芯片。在同一個機箱里面的容量更是從以前的25億門擴大到現在的大約37.5億門。”李立基舉例說。

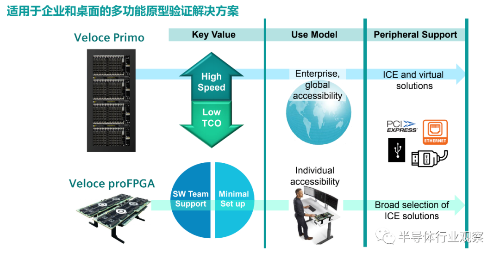

此外,Siemens EDA的這個系統還包括了Veloce Primo和Veloce proFPGAFPGA 這兩個原型驗證系統,其中Primo是企業級的,proFPGA則是桌面的。

首先看企業級系統Veloce Primo方面,據了解,這是一個可以被放到數據中心里面,允許很多不同的用戶同時去分享的系統。它的好處就是高速度和較低的總體擁有成本(TCO),因為你可以分享,而且不管放到哪個地方,企業里面不同的部門、不同的設計中心都可以分享。

“這個多用戶的系統最多可以用320個FPGA設計容量,可以做到120億門容量,工作負載較Veloce Strato高出10倍,擁有從7到70+ MHZ的高性能。”李立基說。

至于桌面 FPGA 原型驗證系統Veloce proFPGA,它的好處是靈活性,因為它有不同的方案,同時能夠保證高性能及可用性;它還可以從單一通道擴展到四個通道,最多可以把5個四通道板的桌面proFPGA連到一起,做到8億門的容量。這也讓他們在這個容量上做得非常靈活;它可以最低從40MG擴展到800MG,在不同的組合里面也都可以進行配置。

在演講中,李立基最后強調,Siemens EDA的FPGA原型驗證系統和Strato都很重要的一點就是統一性和互通性。換而言之,就是Strato跟Primo、FPGA都是用統一的操作系統、統一的解決方案、同樣的方法和通用的RTL前端編譯器。所以當你做了一個設計,要把它從Strato搬到Primo或proFPGA上時,RTL是不需要修改的。這就能夠幫助我們的客戶用統一的方法輕松快捷地在不同的系統上做不同的事情。

“Mentor(現在已改名Siemens EDA)早在1998年的時候,就在硬件仿真的領域進行技術探索并推出產品,在2002年收購Ikos公司之后,我們在這一領域的進步越來越快。在經歷了多年的技術演進之后,Veloce平臺成為了一個在芯片、SoC功能及效能驗證方面非常知名且非常重要的品牌。我們推出這套新產品的意義就在于將這些技術演進下去。”凌琳告訴記者。