文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.040

中文引用格式: 史永勝,田衛東,高靜茹,等. 兩級高輕載效率數字功率變換器的研究[J].電子技術應用,2016,42(8):162-165.

英文引用格式: Shi Yongsheng,Tian Weidong,Gao Jingru,et al. Research on two-stage power converter based on digital control with high light load efficiency[J].Application of Electronic Technique,2016,42(8):162-165.

0 引言

電源的輕載效率是當今信息時代電源設備進一步發展的必要關注課題之一。

為提高輕載效率,提出了許多方法:針對移相全橋變換器,文獻[1-3]從死區時間角度出發,引入輔助電路或直接加寬死區時間,這改善了輕載效率,但是電路復雜度和負載實時靈活性降低,加上額外的損耗,限制效率的進一步提升;文獻[4]通過動態調整母線電壓降低開關損耗,但是沒有對后級電路做進一步的研究;文獻[5-6]通過分模式控制,提高了DC/DC部分的輕載效率,但是沒有考慮母線電壓對效率的影響。

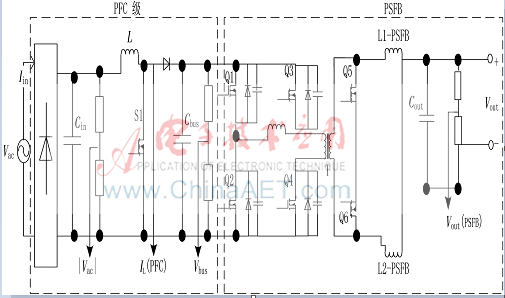

本文研究的兩級變換器如圖1所示,在輕載情況下,母線電壓動態調整在降低開關管應力的同時使移相全橋的占空比保持在最大值,并且全橋部分工作在PWM控制和PWM Burst控制模式下,以進一步減小開關損耗和環路電流損耗;當負載增加到一定值時,全橋變換器改用移相控制。最后,基于TI的DSP平臺(TMS320F28335),設計一臺600 W的試驗樣機驗證控制方法的正確性和有效性。

1 兩級結構及其集成控制系統設計

按照服務器系統架構(Server system architecture,SSI)標準[7],該電源系統分為兩級,前級AC/DC變換器,后級DC/DC變換器,如圖1所示。前級PFC廣泛采用Boost變換器結構[8-9],還要滿足EN61000-3-2等的對電流諧波的要求,同時為達到功率因數校正的目的,對輸入電壓采樣并作為輸入電流的參考值,使輸入電流與輸入電壓同相位;后級移相全橋(PSFB)在無輔助原件條件下完成零電壓開關且適用于大、中功率場合的特點使它在DC/DC部分得到廣泛應用[10]。

圖 1 兩級功率變換器結構圖

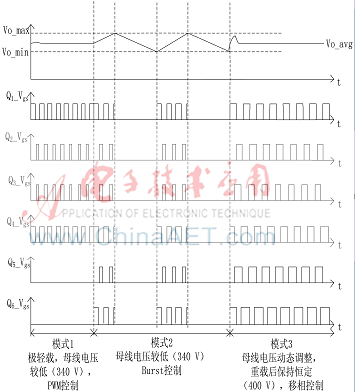

圖2為集成控制時序圖,按照輸出電流值大小主要分為三種模態:模態1,極輕載(0~5%),母線電壓保持在較低水平(340 V),直接采用PWM驅動信號,此時,原副邊的電流都很小,整流體二極管導通損耗極小,原邊幾乎無環流;模態2,輕載(5%~20%),進入PWM Burst控制模式,該模式下,母線電壓還是保持在較低水平(340 V),當輸出電壓超過其額定值的1%不再發出驅動信號,否側有驅動信號,而且,在該模式下的開關頻率低于正常工作開關頻率,且母線電壓值較低,使得輕載主要的開關損耗大大降低;模態3,進入移相控制模式,該模式下能自然實現零電壓開關,且母線電壓動態調整,使占空比保持在最大值,從而減小損耗,提升整體效率,當重載(70%~100%)時母線電壓保持在400 V以滿足重載保持時間的要求[11]。

圖2 集成控制時序圖

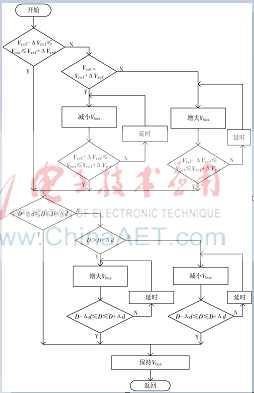

圖3為母線電壓自適應調整流程圖,母線電壓不斷調整使移相全橋的占空比保持在最大值0.48T,0.2T的時間為瞬態裕度和死區時間。

圖3 母線電壓自適應調整流程圖

2 損耗分析

分別對移相控制和PWM控制下的全橋變換器做損耗分析。

2.1 移相控制下的全橋變換器損耗

根據參考文獻[10-11],原邊開關管的關斷損耗Poff_p:

式中,td(off)為開關管關斷時間,Coss_p為原邊開關管等效并聯電容,IPP為原邊峰值電流。

原邊開關管開通損耗為Pon_p:

其中,Ip2為原邊電感續流終止電流。

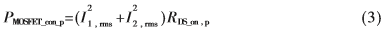

原邊單只開關管通態損耗PMOSFET_con_p:

式中,I1,rms是變壓器正常工作原邊電流有效值, 是原邊環流期電流有效值。

是原邊環流期電流有效值。

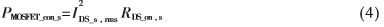

同步整流管的通態損耗PMOSFET_con_s:

式中IDS_s_rms是流過管子的電流有效值,電感和變壓器通態損耗Pinductor_con,PTR_con:

式中IL,rms為電感電流有效值。

磁芯損耗Pcore:

2.2 PWM控制下的全橋變換器損耗

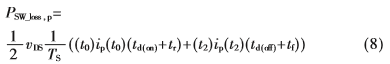

原邊開關管開關損耗PSW_loss,p:

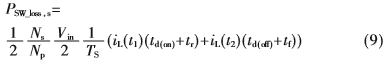

副邊開關損耗PSW_loss,s:

開關管的通態損耗PMOSFET_con_p:

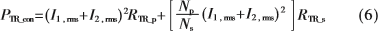

變壓器通態損耗PTR_con:

電感與磁芯損耗見式(5)、式(7)。

2.3 損耗分布與對比

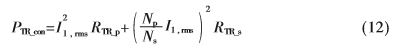

圖4為輕載及極輕載時,一般移相控制和本文集成控制下的損耗對比,集成控制下效率提升了2.14%。

圖4 輕載及極輕載模式下移相控制與集成控制損耗

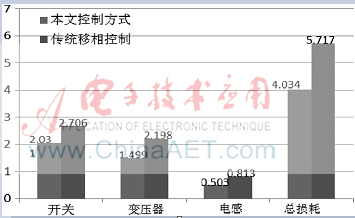

由圖2知,在輕載與極輕載模式下變換器開關管有效工作時序均為PWM信號。結合圖5中變換器理論效率曲線,可知PWM全橋變換器在輕載和極輕載情況下確實能提高變換器的輕載效率。

圖5 效率曲線

3 仿真與實驗分析

首先基于Psim9.0對電路進行了仿真。主要實驗參數設計如下:諧振電感Lr=48  變壓器變比n=54:8,開關頻率fs=100 kHz,死區時間tdead=300 ns。

變壓器變比n=54:8,開關頻率fs=100 kHz,死區時間tdead=300 ns。

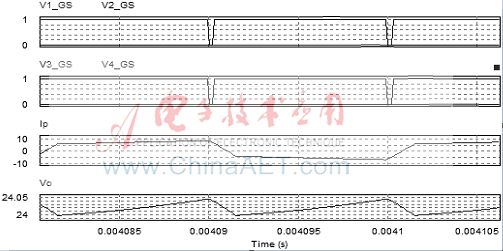

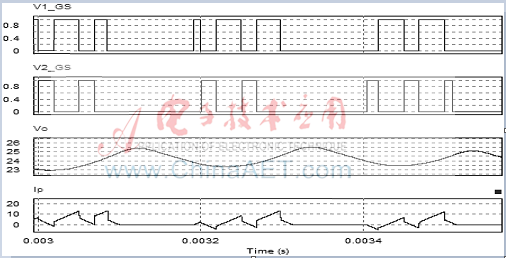

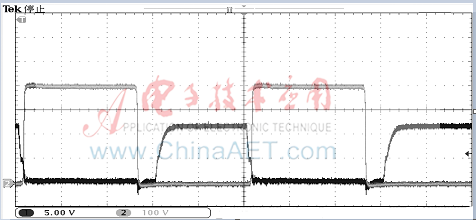

如圖6、圖7分別為輕載和極輕載條件下的工作波形,在仿真基礎上搭建一臺600 W的實驗樣機。實驗表明,該變換器在達到高輕載效率的同時能保證正常工作較大負載范圍內實現ZVS。圖8為Q1驅動波形圖,其他驅動波形類似。

圖6 輕載工作波形

圖7 極輕載工作波形

圖8 Q1零電壓轉換

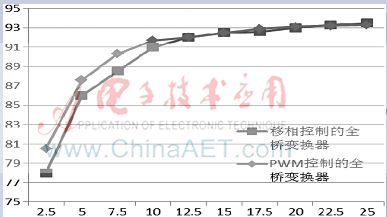

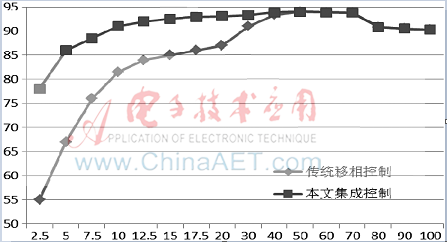

圖9將本文中集成控制下的變換器與傳統全橋變換器的整機效率作比較。可以看出,在低于5%額定負載的情況下,效率能維持在70%以上,5%~20%額定負載情況下效率達到90%以上,遠高于傳統全橋變換器效率。原因在于,本論文搭配輸出電壓可調的PFC并分模態控制變換器,使得變換器具有較高輕載效率。另外,數字控制減少了控制環路器件,減少了整機損耗。

圖9 整機效率

4 結論

本文重點研究了兩級功率變換器的輕載效率,結合數字控制技術提出了一種集成控制策略。在輕載和10%額定負載下效率分別提升了6.9%、10.0%,可以對服務器、適配器等電源的發展起到進一步推動作用。

參考文獻

[1] KIM Y D,CHO K M,KIM D Y,et al.Wide-range ZVS phase-shift full-bridge converter with reduced conduction loss caused by circulate ingcurrent[J].IEEE Transactions on Power Electronics,2013,28(7):3308-3316.

[2] ZHONG C,SHASHA L,LIANGCHEN S.A soft switching full bridge converter with reduced parasitic oscillation in a wide load range[J].IEEE Transactions on Power Electronics,2014,29(2):801-811.

[3] KIM D Y,KIM C E,MOON G W.Variable delay time method in the phase-shifted full-bridge converter for reduced power consumption under light load conditions[J].IEEE Transactions on Power Electronics,2013,28(11):5120-5127.

[4] LAI Y S,SU Z J.Novel on-line maximum duty point tracking technique to improve two-stage server power efficiency and investigation into its impact on hold-up time[J].IEEE Transactions on Industrial Electronics,2014,61(5):2252-2263.

[5] 史永勝,高丹陽,劉言新,等.數字控制DC/DC變換器輕載效率的研究[J].電子技術應用,2015,41(8):113-116.

[6] 史永勝,余彬,王喜鋒,等.基于DSP的高輕載效率數字DC/DC變換器[J].電子器件,2015,38(2):338-342.

[7] 李冬,阮新波.三種服務器電源系統的比較分析[J].中國電機工程學報,2006,26(13):68-73.

[8] JANG Y,JOVANOVIO M M.A bridgeless PFC boost rectifier with optimized magnetic utilization[J].IEEE Transactions on Power Electronics,2009,24(1):85-93.

[9] LAI Y S,YEH C A,HO K M.A family of predictive digitalcontrolled PFC under boundary current mode control[J].IEEE Transactions on Industrial Electronics,2012,8(3):448-458.

[10] 張運成.倍流同步整流移相全橋直流變換器的研究[D].哈爾濱:哈爾濱工業大學,2014:11-18.

[11] LAI Y S,SU Z J,CHEN W S.New hybrid control technique to improve light load efficiency while meeting the hold-up time requirement for two-stage server power[J].IEEE Transactions on Power Electronics,2014,29(9):4763-4775.