前言

調相脈沖信號可以獲得較大的壓縮比,它作為一種常用的脈沖壓縮信號,在現代雷達及通信系統中獲得了廣泛應用。隨著近年來軟件無線電技術和電子技術的發展,DDS(直接數字頻率合成)用于實現信號產生的應用越來越廣。DDS技術從相位的概念出發進行頻率合成,它采用數字采樣存儲技術,可以產生點頻、線性調頻、ASK、PSK及FSK等各種形式的信號,其幅度和相位一致性好,具有電路控制簡單、相位精確、頻率分辨率高、頻率切換速度快、輸出信號相位噪聲低、易于實現全數字化設計等突出優點。

目前,DDS的ASIC芯片如AD公司的AD9852、AD9854等,對于相位調制信號,可方便地產生BPSK,但是,對QPSK或8PSK等則實現困難,它們對控制更新脈沖要求極高,一旦偏差超過DDS內極高的系統時鐘,輸出相位就會錯誤。本文介紹了一種通過FPGA實現QPSK或更高階PSK信號的方法,可靈活地通過上位機的PCI總線控制參數,產生不同載波頻率、不同脈沖寬度、不同占空比、不同重復周期等的QPSK信號,對雷達等系統的設計者具有很好的借鑒意義。

QPSK信號源的設計方案

DDS原理

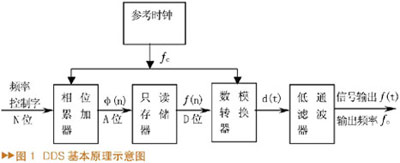

DDS是一種全數字化的頻率合成器,由相位累加器、正弦波形ROM存儲器、D/A轉換器和低通濾波器構成,其基本原理如圖1。

輸出信號的頻率為fout=fclk·Δφ/2N,而最小頻率分辨率為Δfo=fomin=fo/2N,可見改變頻率控制字N即可改變輸出信號的頻率。當參考時鐘頻率給定后,輸出信號的頻率取決于頻率的控制字,頻率分辨率取決于累加器的位數,相位分辨率取決于ROM的地址線位數,幅度量化取決于ROM的數據字長和D/A轉換器的位數。

為了提高DDS輸出信號的頻譜指標和降低正弦的ROM存儲器,近來發展了如在相位截斷后加數字反sinc濾波,利用三角函數對稱性只存取1/4周期查找表,基于CORDIC、泰勒級數加權的頻率合成方法等技術。

QPSK信號源的設計方案

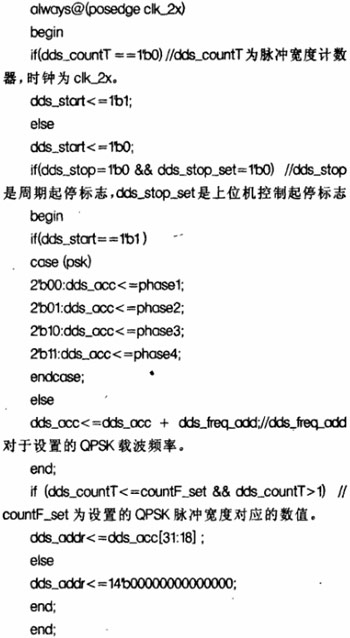

在FPGA中,通過正弦查找表和相位累加器實現DDS,通過計數器實現QPSK信號的起停控制。在計數器計數到零時,設置標志位,讀取寄存器中的QPSK控制碼,從而設置初始相位。在計數到根據QPSK脈沖寬度設定的值后,計數器置0并重新開始計數。運行完設置碼元的個數及次數后,使能輸出禁止標志位。

QPSK信號的重復周期也通過計數器實現。根據周期的范圍和系統時鐘,設置計數器的位數并使其滿足要求。在計數器計數到設定值后,清除輸出禁止的標志位。需要注意的是周期計數器應該與QPSK碼元寬度計數器同步。

QPSK信號參數控制通過PCI總線實現,包括QPSK信號的開始、結束、碼元個數、次數、碼字以及QPSK信號重復周期等。在FPGA內通過寄存器讀取、保存參數。

硬件設計

系統組成與結構

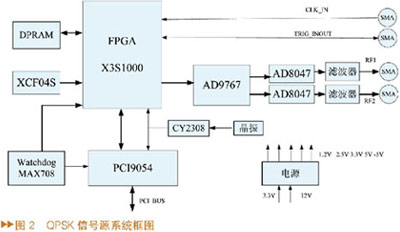

FPGA選用XILINX公司Spartan3系列的XC3S1000,為100萬門大規模可編程器件。它內部具有432kbit的Block Ram和120kbit的Distributed Ram;4個時鐘管理單元DCM;24個乘法器。配置采用XILINX的專用PROM XCF04S,4M位的串行Flash PROM。XC3S1000通過XCF04S實現主串配置,M0、M1、M2均置低。系統框圖如圖2。

高速DAC選用AD公司的AD9767,它是雙通道14位精度的高速CMOS DAC。它內部集成1.2V的電壓基準,SFDR和IMR可達83dBc,最高轉換率為125MSPS,滿量程電流可調范圍為2mA~20mA,兩路D/A輸出后經兩片高速、寬帶放大器AD8047放大,然后經濾波器輸出,AD8047增益為1,實現電流到電壓的轉換。

PCI接口芯片采用PCI9054,是PlX公司應用廣泛的32位、33MHz的PCI橋芯片,實現PCI總線和本地總線的轉換。PCI9054可工作在主、從模式,支持DMA,支持猝發操作。PCI9054的上電通過2k位的EEPROM NM93CS56配置,包括PCI9054的本地總線控制、PCI配置空間寄存器的配置等。PCI9054在PCB設計中應注意PCI總線和時鐘的長度約束。

為了提高板上的存儲容量,FPGA通過CYPRESS的CY7C1372C-200擴展了(512k×36)/1M×18位的ZBT SRAM。以零等待狀態讀寫速率可達200MHz,最大訪問時間為3ns,支持Burst操作,適用高速的數據讀寫。

系統通過SMA外接時鐘,同時內部50MHz晶振經時鐘緩沖芯片CY2308輸出,分別作為PCI9054和FPGA的本地時鐘。外接時鐘的輸入阻抗為50Ω,注意通過信號源提供時鐘時應使其峰峰值在2V以上。

復位電路采用MAXIM的看門狗及電壓監控芯片MAX708實現。

電源由PCI總線提供,3.3V電壓直接從PCI總線的3.3V引出,通過凌特公司的LT1764實現2.5V電壓,采用TI公司的TPS54612實現1.2V電壓,分別作為FPGA的輔助電壓Vccaux和核電壓Vccint。TPS54612輸入電壓為3-6V,在3.3V、5V均可使用,輸出可高達6A,且開關控制器內部集成FET場效應管,方便應用。AD8047的正負電壓輸入分別為+5V和-5V,分別由從PCI總線接入的+12V和-12V電壓經穩壓器7805和7905提供。

軟件設計

QPSK信號的生成

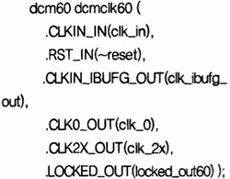

QPSK信號產生的原理在前面已作詳述,FPGA的外接60MHz時鐘通過內部的時鐘管理器倍頻實現120MHz時鐘,通過Block RAM資源實現只讀ROM,然后通過累加器進程、讀QPSK碼字進程、重復周期計數進程等實現DDS功能,通過乘法器還可實現輸出信號的幅度控制。以下是部分源程序,采用Verilog HDL語言編寫。

時鐘管理單元,使用XILINX的DCM實現倍頻,由60MHz變為120MHz。

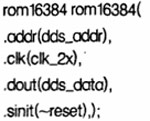

單口只讀ROM,使用IP核,實現正弦查找表,數據寬度為14位,深度為16384字(14地址位)。ROM核接收的數據文件為COE文件,然后轉換為mif二進制文件格式,COE文件可通過C語言或MATLAB生成。ROM核的實現如下:

相位累加器位數設置為32位,系統時鐘120MHz,這樣可實現小于0.03Hz的頻率分辨率,查找表相位截取低14位。累加器進程如下:

DDS信號的控制實現

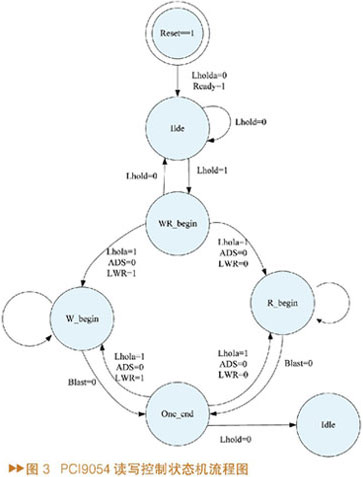

上位機通過PCI總線實現信號參數的讀寫控制。因本系統中只需PCI實現信號參數的控制,數據量不大,故配置PCI9054為PCI的從目標(Slave),C模式。

在FPGA中實現參數寄存器,實時讀取PCI總線的數據并更新。FPGA本地總線的讀寫通過三態門控制。實現代碼如下:

讀寫實現通過狀態機程序實現,讀寫狀態流程圖如圖3。

上位機程序設計

上位機安裝Windows系統,傳統上,PCI的驅動通過微軟的DDK實現WDM驅動程序,本信號源設計中采用Windriver軟件,可方便地讀寫主機給PCI9054系統板分配的內存及I/O資源,并可生成inf文件和基于VC等開發環境的程序文件。

結論

試驗表明,以本文所介紹的方法產生的信號源具有很好的性能,5MHz時連續波點頻的雜散SFDR達到70dB以上,輸出信號的頻率覆蓋短波波段,可達30MHz以上。在實際應用中,還可以加上線性調頻等其他信號形式。若信號頻段在超短波以上,可用DDS產生固定中頻,經數字上變頻和DAC芯片(如AD公司的AD9857)上變頻后輸出,該方法具有很強的可擴展性。