通過對可編程邏輯器件CPLD用VHDL語言進行編程,實現(xiàn)編碼譯碼過程,本設計采用HDB3碼對可編成邏輯器件進行編程。

1 CPLD相關內(nèi)容及信道編解碼

CPLD(Complex Programmable Logic Device)是復雜可編程邏輯器件的簡稱,它是20世紀90年代初期出現(xiàn)的高密度可編程邏輯器件,采用E2CMOS工藝制作,一般由三種可編程電路組成,即可編程邏輯宏單元,可編程輸入/輸出單元和可編程內(nèi)部連線。它可利用EDA技術(shù)中的MAX+ PLUS2作為開發(fā)工具,將設計的電路圖或硬件描述語言編寫的程序綜合成網(wǎng)表文件寫入其中,制成ASIC芯片。CPLD的突出優(yōu)點是可反復編程,集成度非常高,數(shù)據(jù)速率快,同時具有較大的靈活性。

2 編碼器的VHDL建模與程序設計

2.1 HDB3碼編碼規(guī)則

HDB3碼是AMI碼的改進型,稱為三階高密度雙極性碼,它克服了AMI碼的長連0串現(xiàn)象。HDB3碼的編碼規(guī)則為先檢查消息代碼(二進制)的連0串,若沒有4個或4個以上連0串,則按照AMI碼的編碼規(guī)則對消息代碼進行編碼;若出現(xiàn)4個或4個以上連0串,則將每4個連0小段的第4個0變換成與前一非0符號(+1或-1)同極性的V符號,同時保證相鄰Y符號的極性交替(即+1記為+V,-1記為-V);接著檢查相鄰V符號間非0符號的個數(shù)是否為偶數(shù),若為偶,則將當前的V符號的前一非0符號后的第1個0變?yōu)?B或-B符號,且B的極性與前一非0符號的極性相反,并使后面的非0符號從V符號開始再交替變化。

2.2 HDB3編碼器的VHDL建模與程序設計

HDB3碼的VHDL建模思想是在消息代碼的基礎上,依據(jù)HDB3編碼規(guī)則進行插入“V”符號和“B”符號的操作,且用2位二進制代碼分別表示。最后完成單極性信號變成雙極性信號的轉(zhuǎn)換。其編碼模型如圖1所示。

信道編解碼器的設計與實現(xiàn)" src="http://files.chinaaet.com/images/20110530/6fffbf6b-6f0c-4aa2-b7e9-09155af419aa.jpg" />

2.2.1 插“V”模塊的實現(xiàn)

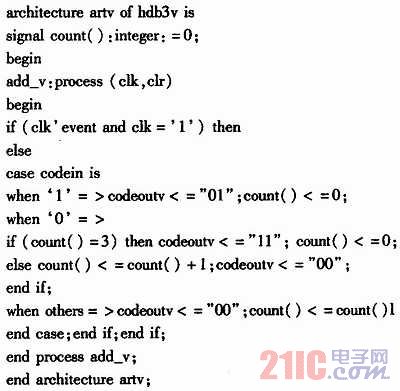

插“V”模塊主要是對消息代碼里的四連0串的檢測,即當出現(xiàn)四個連0串的時候,把第四個“0”變換成符號“V”,用“11”標識。“1”用“01”標識,“0”用“00”標識。實現(xiàn)的VHDL結(jié)構(gòu)代碼如arty:

2.2.2 插“B”模塊的實現(xiàn)

插“B”模塊的建模思路是當相鄰“V”符號之間有偶數(shù)個非0符號時,把后一小段的第1個“0”變換成一個“B”符號。可用一個4位的移位寄存器來實現(xiàn)延遲,這樣經(jīng)插“V”處理過的碼元,可在同步時鐘的作用下同時進行是否插“B”的判決,等到碼元從移位寄存器里出來的時候,就可以決定是應該變換成“B”符號,還是照原碼輸出。輸出端用“11”表示符號“V”,“01”表示“1”碼,“00”表示“0”碼,“10”表示符號“B”。VHDL的結(jié)構(gòu)代碼如artb:

2.3 單極性變雙極性的實現(xiàn)

因為經(jīng)過插“B”模塊后,“V”、“B”、“1”已經(jīng)分別用雙相碼“11”、“10”、“01”標識。“0”用“00”標識。而在實際應用中,CPLD或FPGA端口的輸出電壓只有正極性電壓,且在波形仿真中也只有“+1”和“0”,而無法識別“-1”。所以要得到所需HDB3編碼的結(jié)果,需定義“00”、“01”、“10”來分別表示“0”、“-1”、“+1”。可將插“B”模塊后輸出的“00”、“01”、“10”、“11”組合轉(zhuǎn)換為“00”、“01”、“10”組合,再通過“00”、“01”、“10”控制四選一數(shù)字開關的地址來選擇輸出通道,就可以實現(xiàn)0、-B、+B。本設計使用CC4052的一組通道作為四選一數(shù)字開關,從而將CPLD或FPGA目標芯片的標識性輸出轉(zhuǎn)換成雙極性信號,最終實現(xiàn)HDB3非歸零編碼。

2.4 HDB3編碼器的仿真

在此,以四連“0”的可能性通過多“0”消息代碼進行分析,并利用EDA工具對VHDL源程序進行編譯、適配、優(yōu)化、邏輯綜合與仿真。仿真結(jié)果顯示其完全可以達到編碼要求。而將HDB3編碼硬件描述下載到CPLD或FPGA目標芯片中,然后連接好CC4052進行實際應用測試(用示波器測得)的編碼波形如圖2所示。

3 實驗結(jié)果

利用QUARTUS2開發(fā)工具進行編譯和仿真,HDB3碼器仿真波形如圖3所示。

4 結(jié)論

本設計主要是通過用VHDL語言對可編程邏輯器件CPLD進行控制,基于Altera公司的Quartus X軟件開發(fā)平臺,以原理圖和VHDL語言方法混合輸入設計,實現(xiàn)了信道編碼、HDB3碼和卷積碼的編解碼過程。該設計方案與專用的基帶傳輸碼型編碼芯片相比,有以下優(yōu)勢:體積小,集成度高,開發(fā)周期短,設計過程簡單便捷,運行速度快,使用方便,成本低。本文設計的編碼器能夠彌補專用基帶傳輸碼型編碼芯片的不足,具備一定的工程應用價值。