一、硬件電路設(shè)計(jì)

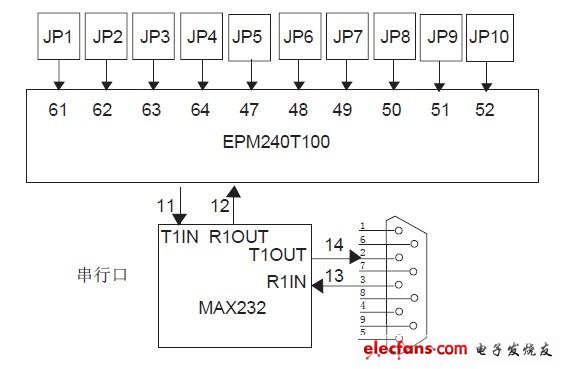

本文選用CPLD 是ALTERA 公司的EPM240T100,結(jié)合MAX232 接口芯片進(jìn)行串口通信設(shè)計(jì),框圖如下圖1 所示。

圖1 CPLD串口通信模塊硬件設(shè)計(jì)

二、VHDL程序模塊設(shè)計(jì)及描述

使用VHDL 對(duì)CPLD 進(jìn)行編程,設(shè)計(jì)3 個(gè)模塊,波特率發(fā)生模塊,接收器,發(fā)送器。

1. 波特率發(fā)生模塊

波特率發(fā)生器實(shí)際是一個(gè)分頻器,如前所述,本文設(shè)計(jì)的波特率為19.2kb/ 秒,設(shè)計(jì)使用的時(shí)鐘頻率為10MHz,所以計(jì)數(shù)器進(jìn)行計(jì)數(shù)時(shí)計(jì)數(shù)到260進(jìn)行翻轉(zhuǎn)。

程序如下(關(guān)鍵部分保留,非必要部分用……代替):

……

ENTITY uart IS

GENERIC(d_len:INTEGER:=8);

PORT (

f10MHz:IN STD_LOGIC;-- 系統(tǒng)時(shí)鐘

reset:IN STD_LOGIC;-- 復(fù)位信號(hào)

rxd:IN STD_LOGIC; -- 串行接收

txd:OUT STD_LOGIC;-- 串行發(fā)送

);

END uart;

ARCHITECTURE behav of uart IS

……

BEGIN

rxds<=rxd;

PROCESS(f10MHz,reset)

-- 設(shè)置波特率發(fā)生器 19200kb/s

VARIABLE clk19200hz: STD_LOGIC;

VARIABLE count:INTEGER RANGE 0 TO 260;

BEGIN

IF reset='0' THEN

count:=0;

clk19200hz:='0';

ELSIF f10MHz'EVENT AND f10MHz='1' THEN

IF count=260 THEN

count:=0;clk19200hz:= NOT clk19200hz;

ELSE

count:=count+1;

END IF;

END IF;

baud_rate<=clk19200hz;

END PROCESS;發(fā)送模塊e#2. 發(fā)送模塊

發(fā)送部分采用狀態(tài)機(jī)t_state 進(jìn)行編程,共設(shè)兩個(gè)值:t-start 和t_shift,分別表示發(fā)送開始以及發(fā)送保持狀態(tài)。復(fù)位鍵按下時(shí)設(shè)置到t-start 狀態(tài),并將發(fā)送數(shù)據(jù)位設(shè)為“1”, 發(fā)送的數(shù)據(jù)位數(shù)計(jì)數(shù)為0,在t-start 狀態(tài),狀態(tài)機(jī)將處于這一個(gè)狀態(tài)并等待波特率計(jì)數(shù)信號(hào)的電平上升沿到來。上升沿到來時(shí),依據(jù)t_state 狀態(tài)的不同值做不同處理,如果是t-start 開始狀態(tài)則先讀待發(fā)送的數(shù)據(jù),并發(fā)送開始位“0”,然后將狀態(tài)轉(zhuǎn)到發(fā)送保持t_shift 狀態(tài),在發(fā)送保持t_shift 狀態(tài),不斷判斷發(fā)送的數(shù)據(jù)位數(shù)是否滿8 位,如果滿了則回歸t-start 狀態(tài),否則繼續(xù)發(fā)送,保持在t_shift 狀態(tài),為避免干擾將其余情況下的狀態(tài)自動(dòng)跳轉(zhuǎn)到t-start 狀態(tài)。程序如下:

PROCESS(baud_rate,reset,data)

-- 數(shù)據(jù)發(fā)送部分

VARIABLE t_no:INTEGER RANGE 0 TO 8;

-- 發(fā)送的數(shù)據(jù)各位的位序號(hào)

VARIABLE txds:STD_LOGIC;

VARIABLE dtmp:STD_LOGIC_VECTOR(7

DOWNTO 0);

BEGIN

IF reset='0' THEN

t_state<=t_start;

txds:='1';

t_no:=0;

ELSIF baud_rate'event AND baud_rate='1' THEN

CASE t_state IS

WHEN t_start=>

dtmp:=data;

txds:='0'; -- 發(fā)送開始

t_state<=t_shift;

WHEN t_shift=> IF t_no=d_len THEN

txds:='1'; -- 發(fā)送結(jié)束

t_no:=0;

t_state<=t_start;

ELSE

txds:=dtmp(t_no); -- 發(fā)送一字節(jié)數(shù)據(jù)

t_no:=t_no+1;

END IF;

WHEN thers=>t_state<=t_start;

END CASE;

END IF;

txd<=txds;

END PROCESS;

3. 數(shù)據(jù)接收模塊

接收部分采用狀態(tài)機(jī)進(jìn)行編程,共設(shè)兩個(gè)狀態(tài):

r-start 和r_shift 分別表示接收開始以及接收保持狀態(tài);復(fù)位鍵按下時(shí)設(shè)置到r-start 狀態(tài),并將待接收存放數(shù)據(jù)的data 賦值為“00000000”, 在r-start狀態(tài),接收狀態(tài)機(jī)將處于這一個(gè)狀態(tài)并等待波特率計(jì)數(shù)信號(hào)的電平上升沿到來。波特率發(fā)生模塊的計(jì)數(shù)上升沿到來,依據(jù)狀態(tài)的不同值做不同處理,如果是r-start 接收開始狀態(tài)則等待開始位信號(hào),檢測(cè)到rxds=‘0’的開始位信號(hào)好轉(zhuǎn)到r_shift 接收保持狀態(tài),r_shift 接收保持狀態(tài)會(huì)不斷判斷接收的數(shù)據(jù)位數(shù)是否滿8 位,如果滿了則回歸r-start 狀態(tài),否則繼續(xù)接收,保持在r_shift 接收保持狀態(tài),為避免干擾將其余情況下的狀態(tài)自動(dòng)跳轉(zhuǎn)到r-start 接收開始狀態(tài),程序與發(fā)送部分類似,此處省略。

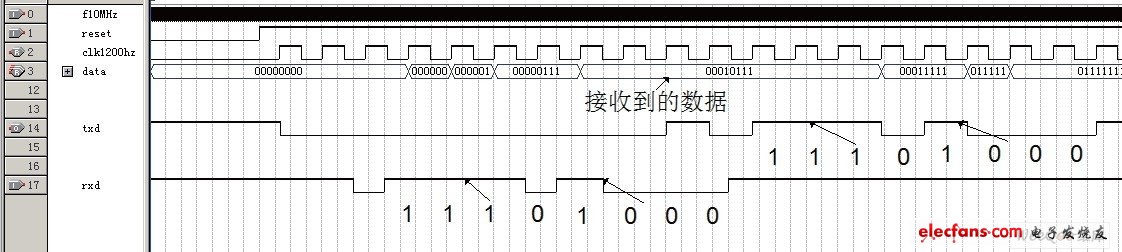

三、串口通信的VHDL程序仿真結(jié)果

串行口通信的仿真結(jié)果如圖2 所示。從圖中可以看出,每發(fā)送完一個(gè)字節(jié),即8 位數(shù)據(jù)后,線路上將輸出一個(gè)高電平,之后又開始傳送下一個(gè)字節(jié)。

同樣,仿真波形顯示,有效數(shù)據(jù)到達(dá)接收管腳rxd之前,線路上保持為高電平,直到收到一個(gè)低電平起始位,將該起始位后的8 位數(shù)據(jù)串行接收后依次送到保存接收結(jié)果的信號(hào)data 的各位。

圖2 串行口通信仿真波形圖

串口通信的硬件驗(yàn)證

將程序通過在系統(tǒng)編程下載入配套的CPLD 電路板進(jìn)行硬件驗(yàn)證,按照以下步驟進(jìn)行。

(1)確定管腳對(duì)應(yīng)關(guān)系:

串行接收管腳rxd 與max232 的12 腳R1OUT對(duì)應(yīng); 串行發(fā)送管腳txd 與max232 的11 腳T1IN對(duì)應(yīng);復(fù)位信號(hào)reset 與按鍵S1 對(duì)應(yīng)。

(2)由QUARTUS II 進(jìn)行管腳分配:

f10MHz 在MAXII 芯片上對(duì)應(yīng)的管腳號(hào)為12 ;S1 在MAXII 芯片上對(duì)應(yīng)的管腳號(hào)為21 ; rxd 在MAXII 芯片上對(duì)應(yīng)的管腳號(hào)為89; txd 在MAXII 芯片上對(duì)應(yīng)的管腳號(hào)為90。

(3)電平定義:

按鍵S1 按下時(shí)表示輸入信號(hào)為低電平。

應(yīng)用“ 串口調(diào)試助手” 進(jìn)行驗(yàn)證, 在發(fā)送窗口隨機(jī)輸入需要發(fā)送的字符,可以發(fā)現(xiàn)由PC 機(jī)發(fā)給CPLD 的字符被CPLD 傳送回來并在接收窗口顯示出來。在批量隨機(jī)數(shù)據(jù)發(fā)送后分析:在傳輸時(shí)19.2kb/s 傳輸速率下,誤碼率達(dá)10-8。