0 引 言

跳頻" title="跳頻">跳頻技術(shù)作為軍事通信的主要抗干擾手段,近幾十年來,在軍事通信裝備中得到了廣泛的應用。20世紀90年代初,出現(xiàn)了高數(shù)據(jù)率抗干擾的短波跳頻系統(tǒng),其跳頻速度達到幾千跳/秒,具有很強的抗多徑、抗衰落能力。在不用自適應均衡的情況下,可提供上千比特/秒的數(shù)據(jù)傳輸能力,所以高速短波跳頻技術(shù)是軍用短波跳頻系統(tǒng)發(fā)展的方向。

在短波高速跳頻系統(tǒng)中,跳頻頻率合成器" title="頻率合成器">頻率合成器的研究是關(guān)鍵技術(shù)之一。從頻率合成技術(shù)的發(fā)展過程看,頻率合成的方法主要有三種:直接頻率合成(DFS)、鎖相環(huán)式頻率合成(PLL)、直接數(shù)字頻率合成(DDS)。這三種基本的頻率合成方法各有特點,實際應用中,采用單獨一種方法往往難以滿足頻率合成器的所有技術(shù)指標。因此,在設計頻率合成器時,可以根據(jù)具體的設計要求,組合使用這些基本方法,以達到最佳的效果。這里的跳頻頻率合成器設計采用了DDS和PLL相結(jié)合的方法。

1 跳頻頻率合成器硬件設計

1.1 方案選擇

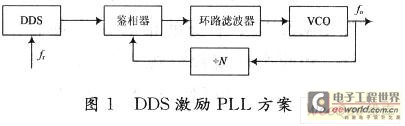

DDS和PLL相結(jié)合構(gòu)成的跳頻頻率合成器有幾種方式:DDS激勵PLL方案、PLL內(nèi)插DDS組合方案和頻率轉(zhuǎn)換快捷的組合方案等。本設計采用的是第一種方案,如圖1所示。PLL設計成N倍頻環(huán),DDS輸出直接作為PLL的參考信號。

該方案主要性能如下:

(1)輸出頻率:f0=NfDDS;

(2)輸出頻率分辨率:fr=NfDDSr(FDDSr為DDS的頻率分辨率);

(3)輸出頻率fo的建立時間:T=TDDS+TPLL。式中:TDDS是改變DDS輸出頻率fDDSr所需的時間;TPLL是fDDS改變后,鎖相環(huán)重新鎖定所需的時間。為了使鎖相環(huán)能很快地鎖定,在鎖相環(huán)的快捕帶寬范圍內(nèi)變化fDDS,這樣TPLL就是快捕時間。通常快捕時間很短,即使變化范圍超出鎖相環(huán)的快捕帶寬范圍,由于這是在上一次鎖定的基礎上重新進行的鎖定過程,所以,鎖定時間也會很短。這樣,輸出頻率fo總的建立時間T就小,可以滿足快速跳頻的需要。

1.2 硬件設計

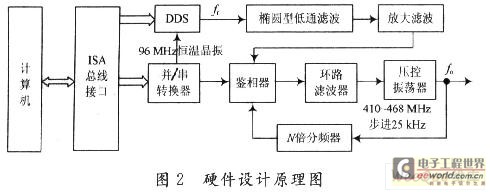

硬件設計原理圖如圖2所示。

圖2為超短波跳頻收發(fā)系統(tǒng)" title="收發(fā)系統(tǒng)">收發(fā)系統(tǒng)中跳頻頻率合成器設計原理圖。系統(tǒng)對跳頻頻率合成器的設計要求:工作頻率為410~468 MHz,頻率間隔25 kHz,可實現(xiàn)全頻段跳頻和分頻段跳頻,頻率轉(zhuǎn)換時間小于100μs。

設計中,DDS的核心器件采用美國AD公司的AD9850;鑒相器采用美國國半(National Semiconduc-tor)的集成鎖相電路LMX2306;VCO選用的是AM-PLIFONIX公司的集成模塊TOM9307,它的輸出信號頻率為300~600 MHz;控制靈敏度為20 MHz/V。

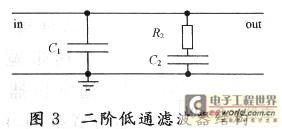

AD9850是采用并行傳輸方式從計算機接收頻率和相位控制字的,這是因為考慮到并行方式傳輸?shù)乃俣缺却蟹绞娇臁?偣?0位控制字,通過8位數(shù)據(jù)總線送到AD9850的輸入寄存器中,需重復5次。在FQUD信號上升沿調(diào)入40位控制字,同時把地址指針復位到第一個寄存器。接著在W_CLK信號的上升沿到來時,把最高的8位數(shù)據(jù)裝入第一個寄存器,并把地址指針指向下一個寄存器。這樣,連續(xù)5個W_CLK上升沿后,就把40位控制字都裝入了寄存器,W_CLK信號不再起作用,直到收到復位信號或FQ_UD信號的上升沿時,才重新開始新一輪的數(shù)據(jù)裝入。鑒相器LMX2306本身就帶有一個前置雙模分頻器(8/9分頻)和兩個可編程分頻器N,R,采用串行輸入的方式。在初始化時只要給N寄存器、R寄存器和F功能寄存器輸入正確的數(shù)據(jù),就可以正常工作了。LMX2306的外部環(huán)路濾波器在鎖相環(huán)路中起非常重要的作用,環(huán)路濾波器形式和參數(shù)的選取是鎖相環(huán)設計與調(diào)試的關(guān)鍵,在很大程度上決了定環(huán)路的噪聲、捕獲和跟蹤性能等。該環(huán)路濾波器選用二階無源比例積分濾波器,其二階低通濾波器結(jié)構(gòu)如圖3所示。

利用美國國半公司提供的PLL環(huán)路濾波器設計軟件Loopfilt可方便地計算出濾波器的參數(shù),如圖4所示。

在實際電路中,環(huán)路濾波器的參數(shù)選定為:

2 跳頻頻率合成器的性能估算

在分析跳頻頻率合成器的性能時,尤其對于快速跳頻系統(tǒng)來說,頻率分辨率和換頻性能是其中兩個很重要的指標。

在該方案中,跳頻頻率合成器是由DDS激勵PLL組成的。因DDS的系統(tǒng)時鐘為96 MHz,則AD9850的輸出頻率fDDS=96 MHz/232△0.022 35 Hz。鎖相環(huán)PLL的輸出頻率為:

式中:Ntotal為環(huán)路總的分頻比。設計中要使最后的輸出頻率fo在410~468 MHz內(nèi)跳變,頻道間隔為25 kHz。由相關(guān)參考文獻中的公式可算得:R=400 Ω,Ntotal=1*00,即B=2 050,A=0,則編程使fDDS在10~11.414 346 MHz內(nèi)變化,那么fo將在410~468 MHz內(nèi)跳變,其頻率分辨率(單位Hz)為:

該跳頻頻率合成器總的跳頻轉(zhuǎn)換時間也應該是這兩部分跳頻轉(zhuǎn)換時間之和。DDS的換頻時間很短,對AD9850來說,是ns級的,幾乎可以忽略不計。所以整個跳頻頻率合成器的跳頻轉(zhuǎn)換時間主要由PLL的跳頻轉(zhuǎn)換時間決定。

在工程上,PLL的跳頻轉(zhuǎn)換時間可以用PLL環(huán)路的最大快捕時間TLmax做估算:

設計中,ωn=15 000×2π;工程上ξ=0.707,則TLmax△75μs。所以,頻率建立時間TPLL=75μs,跳頻周期可為750μs,跳頻速率最高可達1 333跳/s,滿足系統(tǒng)設計的1 000跳/s的要求。

3 結(jié)語

跳頻頻率合成器是跳頻收發(fā)系統(tǒng)設計的核心,也是技術(shù)實現(xiàn)的一個難點。設計中把DDS和PLL的優(yōu)點有機地結(jié)合起來實現(xiàn)了高速跳頻,摒棄了用直接數(shù)字頻率合成DDS輸出頻率不能太高或用鎖相環(huán)PLL合成頻率鎖定時間較長的缺點,滿足了系統(tǒng)設計的要求。