數據采集在現代工業生產及科學研究中的重要地位日益突出,對實時高速數據采集的要求也不斷提高。在信號測量、圖像處理、音頻信號處理等一些高速、高精度的測量中,都要求進行高速、高精度的數據采集。這就對數據采集系統的設計提出兩個方面的要求:一方面,要求接口簡單靈活且有較高的數據傳輸率;另一方面,由于數據量通常都較大,要求主機能夠對數據做出快速反應,并及時分析和處理。

實現數據采集與傳輸,可選擇如下3種方法:

①使用傳統的串/并口。傳統的串口(如RS232),其傳輸速率為幾十kb/s到100 kb/s,而系統所要求的數據傳輸速率很高,而且還要實現數據的采集與傳輸同步進行,串口的速率遠遠達不到實時要求;對于并口,雖然它的傳輸速率可達到1 Mb/s以上,但由于探測器與主機相距較遠,因此走線比較復雜。

②采用通用的高速數據采集卡。高速數據采集卡(如ISA或PCI卡)雖然在數據存取速度上可滿足系統要求,但仍然存在很多缺點,比如安裝復雜,價格昂貴,兼容性不好,受計算機插槽數量、地址和中斷資源的限制,可擴展性較差等。

③使用USB2.0通用串行接口總線。USB接口是一種重要的計算機外設接口,它支持熱插拔和即插即用,使用非常方便。USB2.0支持高達480 Mbps的數據傳輸速率。USB接口可實現計算機與多個外圍設備的簡單、高速互聯,將USB技術應用于數據采集是非常適合的。經綜合考慮,本文選擇采用USB2.0接口來完成對數據的采集與傳輸。

1 數據采集和傳輸系統方案設計

數據采集和傳輸系統主要由3部分組成,USB2.0通道、FPGA和A/D轉換器組成,如圖1所示。

CY7C68013是Cypress公司推出的EZ-USB FX2系列智能USB接口芯片。其作用是將主機所發送的命令序列經USB2.0端口輸出,實現對數據采集系統的控制;同時把A/D轉換器采集的數據以高速的數據序列形式發送到主機。其中,USB2.0端口提供一個能和計算機連接的數據傳輸接口。

FPGA利用內部的SRAM提供數據輸入/輸出的雙緩沖功能。采用雙緩沖的原因同USB中的大端點所配置的雙緩沖類似,均是防止數據的溢出和保證數據傳輸的連續性。本文選用Altera公司的CycIone系列芯片EP1C3T144。

A/D轉換器將所要采集的模擬量轉換成數字量,通過濾波和放大后,由FPGA接收、緩沖、存儲,經USB2.0端口傳回至主機工作站。高速A/D轉換器采用轉換速率為20 MHz的MAX1425。

系統工作過程為:主機通過CY7C68013給數據采集系統一個采樣控制命令,存入FPGA的控制寄存器中。FPGA根據該命令向A/D轉換器發出相應控制信號。由于ADC采樣頻率為10 MHz,為和PC運行速度相匹配,在FPGA內部生成一個FIFO緩存器。A/D轉換器在FPGA的ADC接口控制電路控制下,把模擬信號轉換成數字信號,并將指定通道的采樣數據存入FPGA內部FIFO緩存。同時,FPGA的USB接口控制邏輯查詢CY7C68013是否空閑,如果空閑,那么由FPGA的USB接口控制邏輯將指定通道的采樣結果,從FPGA內部FIFO緩存送入CY7C68013的內部FIFO。當內部的FIFO容量達到一定程度后,CY7C68013自動將數據打包傳送到PC機。由于固件程序把CY7C68013設置為特定的自動模式,因此CY7C68013把數據送往PC機期間的所有操作無需CY7C68013中CPU的干預,從而保證足夠的數據傳輸速率。采樣過程中FPGA的USB接口控制邏輯依次取走批量數據,在USB接口打包傳送時A/D轉換持續進行,FPGA內部FIFO也被持續寫入轉換結果。

2 硬件設計

系統的硬件由A/D轉換電路、數據采集與傳輸控制電路和接口電路構成。

2.1 A/D轉換電路

A/D轉換電路是整個系統的重要組成部分。由低通濾波器、多路選擇開關和A/D轉換器構成,如圖2所示。本文選用Maxim公司的A/D轉換芯片MAX1425。

8路模擬輸入信號分別經過由運放THS4052構成的抗混疊低通濾波器去除高頻成分,防止信號產生“混疊現象”。1/8模擬信號選擇器根據來自FPGA板的地址碼,控制模擬信號選擇器74HC4051選通8路輸入中的1路到輸出端,送到A/D轉換器MAX1425將模擬信號轉換為數字信號。MAX1425的控制信號由FPGA板提供,在控制信號的作用下以適當的時序完成轉換工作。

2.2 數據采集與傳輸控制電路

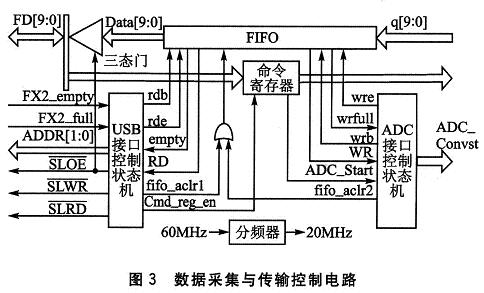

數據采集與傳輸控制電路的開發工作主要集中在FPGA上。FPGA負責CY7C68013與ADC芯片之間的緩沖與控制,一邊與ADC接口,另一邊與USB接口,產生數據采集、通道切換、A/D轉換、FIFO所需的全部控制信號;實現對傳輸數據的緩存、讀/寫控制、時鐘、輸出使能、端點的選擇,以及對ADC的控制等功能。

如圖3所示,數據采集與傳輸控制電路由FIFO、USB接口控制狀態機、ADC接口控制狀態機、三態門緩沖器、控制寄存器組幾部分構成。圖中,由右向左的寬箭頭表示數據流;FD[9:0]是與USB接口芯片連接的雙向數據總線;由左向右的寬箭頭表示傳送來自PC機的控制信號;單線箭頭表示輸入/輸出,以及FPGA內部各個模塊間的控制信號線。

從數據流向看,數據在ADC接口控制狀態機的協調下通過ADC接口送入FPGA的FIFO中。經過FIFO的緩沖后,在USB接口控制狀態機的協調下,當USB接口控制狀態機對三態門的輸出為高時,三態門開啟,數據通過三態門傳輸到FPGA外部的USB接口;當對三態門的輸出為低時,三態門呈現高阻態,FPGA的這幾個引腳作為輸入引腳。此狀態下,來自PC機的控制信號通過CY7C68013從FD[15:0]送人FPGA中。在USB接口控制狀態機的控制下,來自PC機的控制信息存人控制寄存器組,并由ADC接口控制狀態機來控制送往FPGA外的ADC接口,作為對ADC的控制(如通道的選擇)。

2.3 接口電路

2.3.1 FPGA內的ADC接口模塊

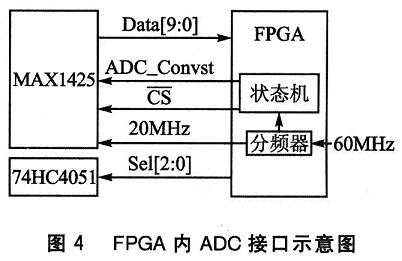

MAX1425和74HC4051的控制信號都由FPGA產生,接口電路如圖4所示。

FPGA的工作時鐘為60 MHz,該時鐘經過分頻后,提供20 MHz給MAX1425作為工作時鐘,同時也作為FP-GA內其他邏輯的工作時鐘。由FPGA內狀態機控制,當CS為低和ADC_Convst為高時,MAX1425進入采樣保持狀態。當Clock的第一個上升沿到來,MAX1425開始轉換。RD輸出為低時,MAX1425把轉換結果放到數據總線上,FPGA開始讀入10位數據(FD[15:0]中的10~15六位數據線懸空,使數據線和A/D的位數匹配)。FPGA控制寄存器的Sel[2:O]信號作為74Hc4051的通道選擇信號,從8路模擬輸入入信號中選擇1路作為MAX1425的輸入。完成一次轉換后,當ADC_Convst:再次為高時,開始下一輪轉換。

2.3.2 FPGA內的USB接口模塊

圖5是Slave模式下CY7C68013與FPGA的連接示意圖。中間是FPGA中USB接口模塊部分對應的信號。

2.3.3 FPGA內的USB接口控制狀態機

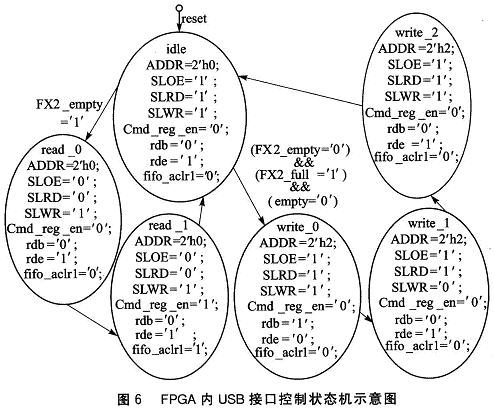

FPGA內USB接口控制狀態機的狀態轉移圖如圖6所示。共有6個狀態,復位信號的模式設置為異步復位。狀態機主要分為讀、寫兩部分:讀取EP2中所包含的命令,存到FPGA的控制寄存器組中;將FPGA的FIFO中的數據讀出,寫入EP6端點緩沖區。

該狀態機工作過程為:

①系統加電或復位后,狀態機進入空閑狀態(idle)。

②在空閑狀態下,當EP2不為空時進入read_0狀態,從EP2中讀出PC機傳來的控制命令。隨后進入read_1狀態,把命令存到FPGA內控制寄存器中,并把FPGA內的FIFO清空(fifo_ach1='1'),以準備存儲采樣數據。之后再回到idle狀態。

③在空閑狀態下,當EP2為空(FX2_empty='0'),而FPGA的FIFO不為空(empty='0'),且EP6不滿時,進入write_0狀態。之所以要看EP2是否為空,是想優先處理PC機通過EP2傳來的命令。在write_0狀態下,選中對CY7C68013的EP6操作(ADDR=2'h2),同時從FPGA內部的FIFO中讀出一個數據。之后進入write_1狀態,把數據寫入CY7C68013。然后進入write_2狀態,write_2狀態的輸出與idle狀態相同,目的是提供一個時鐘周期的延遲。因為FPGA工作于60 MHz的時鐘下,比CY7C68013快,所以加入一個延遲以保證可靠的數據傳輸。

3 軟件設計

如圖7所示,數據采集系統的軟件設計包括3部分;CY7C68013的固件程序、Windows平臺上USB設備驅動程序和應用程序。在Windows操作平臺下,當有新的設備接入時,操作系統就會依據設備回送的有關信息自動地調用相應的設備驅動程序。當USB設備的設備驅動程序裝載后,主機應用程序通過USB設備驅動程序與系統USBDI(USB Device Inte

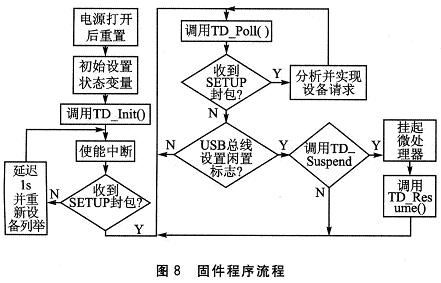

固件架構實現了與USB兼容的外圍設備所需的基本功能。經過鏈接(Iink)最小的描述符表文件,并對該架構作適當的修改或添加部分代,就可以構建出完全兼容的設備固件架構。通過鏈接Cypress公司所提供的子程序,就有可能逐漸地構建出完全兼容功能的設備。固件程序的流程如圖8所示。

4 結 論

基于FPGA和USB2.0的高速實時數據采集系統,采用計算機的USB接口作為數據傳輸接口。軟件設計工作包括MCU的固件程序設計、計算機上USB接口驅動程序設計、計算機上應用程序設計等幾部分。MCU在FPGA和計算機之間起橋梁的作用,既要對USB接口進行控制,實現與計算機的通信,接受計算機的控制,又要對它與FPGA的接口進行設置和控制,還會與FPGA進行對話以實現對FPGA的工作模式進行設置。