引言

傳統(tǒng)的示波器雖然功能齊全,但是體積大、重量重、成本高、等一系列問題使應(yīng)用受到了限制。有鑒于此,便攜式數(shù)字存儲采集器就應(yīng)運而生,它采用了LCD顯示、高速A/D采集與轉(zhuǎn)換、ASIC芯片等新技術(shù),具有很強的實用性和巨大的市場潛力,也代表了當(dāng)代電子測量儀器的一種發(fā)展趨勢,即向功能多、體積小、重量輕、使用方便的掌上型儀器發(fā)展。

系統(tǒng)組成結(jié)構(gòu)及工作原理

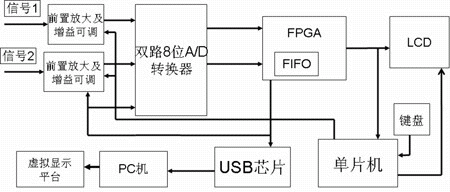

系統(tǒng)的硬件部分為一塊高速的數(shù)據(jù)采集電路板。它能夠?qū)崿F(xiàn)雙通道數(shù)據(jù)輸入,每路采樣頻率可達到60Mbit/s。從功能上可以將硬件系統(tǒng)分為:信號前端放大及調(diào)理模塊、高速模數(shù)轉(zhuǎn)換模塊、FPGA邏輯控制模塊、單片機控制模塊、USB數(shù)據(jù)傳輸模塊、液晶顯示和鍵盤控制等幾部分,其結(jié)構(gòu)形式如圖1所示。

圖1 系統(tǒng)原理結(jié)構(gòu)圖

輸入信號經(jīng)前置放大及增益可調(diào)電路轉(zhuǎn)換后,成為符合A/D轉(zhuǎn)換器要求的輸入電壓,經(jīng)A/D轉(zhuǎn)換后的數(shù)字信號,由FPGA內(nèi)的FIFO緩存,再經(jīng)USB接口傳輸?shù)接嬎銠C中,供后續(xù)數(shù)據(jù)處理,或直接由單片機控制將采集到的信號顯示在液晶屏幕上。

高速數(shù)據(jù)采集模塊

本系統(tǒng)可實現(xiàn)雙通道同步數(shù)據(jù)采集,而且每通道

的采集速度要達到60Mbit/s,考慮到兩路數(shù)據(jù)采集應(yīng)保持同步并行,因此在設(shè)計中采用每通道都有獨自的采樣保持器和A/D轉(zhuǎn)換器。選用MAXIM公司MAX1197型A/D轉(zhuǎn)換器,它是一款雙通道、3.3V供電、每通道60Mbit/s采樣頻率的模數(shù)轉(zhuǎn)換器芯片。它內(nèi)部集成雙路差分寬帶采樣保持器和A/D轉(zhuǎn)換器,可以輸出鎖存,具有低功耗、小尺寸、高動態(tài)性能的特點。

本系統(tǒng)的測量電壓的范圍可達到±300V,采用示波器探頭和電路板上分壓的方法將輸入信號先進行1:1或10:1或100:1衰減,然后再通過后續(xù)電路處理以滿足A/D轉(zhuǎn)換器的輸入電壓范圍要求。

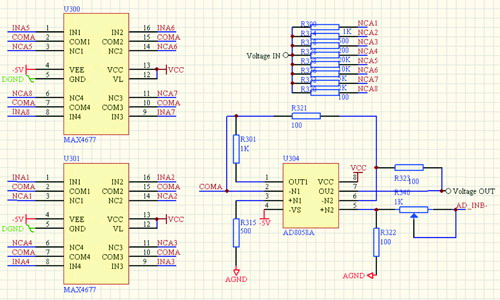

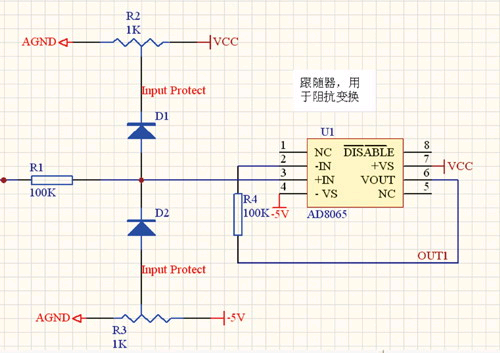

被測信號通過通用探頭和分壓器得到的輸出信號,由于輸出阻抗較高,需要經(jīng)過阻抗變換成為低的輸出阻抗,以保持信號的完整性。同時,對于一個系統(tǒng)來講,過載是不可避免的,在過載情況下,如果沒有保護,器件很容易損壞。因此,系統(tǒng)中設(shè)計了由二極管和電阻構(gòu)成的過載保護電路,將輸入信號限制在±4.8V的范圍之間。對于阻抗變換,選擇ADI公司的高性能FET輸入單電壓反饋放大器AD8065芯片,構(gòu)成跟隨器來實現(xiàn)阻抗變換。經(jīng)過阻抗變換的信號,還要通過增益調(diào)節(jié),在能使輸入到A/D轉(zhuǎn)換器的電壓滿足A/D的輸入電壓要求,采用模擬開關(guān)和寬帶精密放大器配合,由模擬開關(guān)選通不同的接入電阻值,從而實現(xiàn)不同的放大倍數(shù),達到程控放大的目的。增益調(diào)節(jié)電路如圖2所示,輸入保護及阻抗變換電路如圖3所示。

圖2 增益調(diào)節(jié)電路

圖3 輸入保護及阻抗變換電路

FPGA控制單元

可編程邏輯器件FPGA是一種半定制的ASIC,它允許電路設(shè)計者自行編程實現(xiàn)特定應(yīng)用的功能。本設(shè)計采用了原理圖輸入和VHDL語言輸入兩種不同的方法,控制單元承載了大部分控制任務(wù),為各個功能模塊提供相應(yīng)的控制信號以確保整個系統(tǒng)工作的正確性。具體實現(xiàn)如下幾個方面的功能:

分頻電路及產(chǎn)生A/D轉(zhuǎn)換器的控制信號

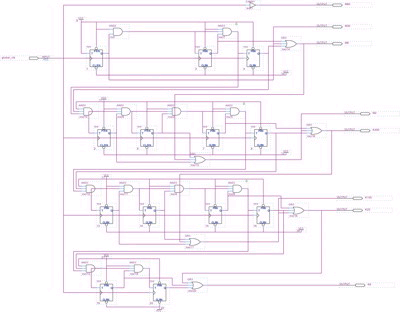

本數(shù)據(jù)采集系統(tǒng),具有比較寬的測量范圍,在FPGA內(nèi)部設(shè)計了一個分頻電路,用來實現(xiàn)針對不同頻率的被測信號選擇不同的采樣頻率,確保采集數(shù)據(jù)更加精確。分頻單元采用圖形輸入方法實現(xiàn)其內(nèi)部結(jié)構(gòu)圖如圖4所示。在圖4中,利用T觸發(fā)器在輸入為1時,每個時鐘沿到來時輸出會發(fā)生跳變來實現(xiàn)分頻的。同時我們可以看出,T觸發(fā)器的輸入是有一些邏輯組合構(gòu)成的,這就構(gòu)成了門控時鐘。對于門控時鐘,仔細(xì)分析時鐘函數(shù),以避免毛刺的影響。而門控時鐘在滿足以下兩個條件時,則可保證時鐘信號不出現(xiàn)危險的毛刺,門控時鐘可以像全局時鐘一樣可靠的工作。

·驅(qū)動時鐘的邏輯必須只包含一個“與”門或一個“或”門。如果采用任何附加邏在某些工作狀態(tài)下,會出現(xiàn)競爭產(chǎn)生的毛刺。

·邏輯門的一個輸入作為實際的時鐘,而該邏輯門的所有其它輸入必須當(dāng)成地址或控制線,它們遵守相對于時鐘的建立和保持時間的約束。

對于本設(shè)計中的A/D轉(zhuǎn)換器,其控制信號只有兩個:時鐘輸入信號CLK和使能輸出信號OE。CLK信號直接通過有源晶振輸入60M的信號,而OE信號則通過FPGA內(nèi)部將和CLK同頻同相的時鐘信號反相后得到,這樣剛好可以滿足A/D轉(zhuǎn)換器的轉(zhuǎn)換時序關(guān)系。

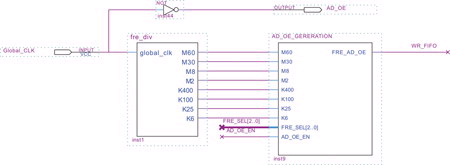

圖4 分頻電路內(nèi)部結(jié)構(gòu)圖

圖5 分頻電路和頻率選擇電路符號圖

上述分頻電路和頻率選擇電路及A/D轉(zhuǎn)換器的控制信號產(chǎn)生電路在頂層生成了相對應(yīng)的邏輯符號如圖5所示。

FIFO功能單元設(shè)計

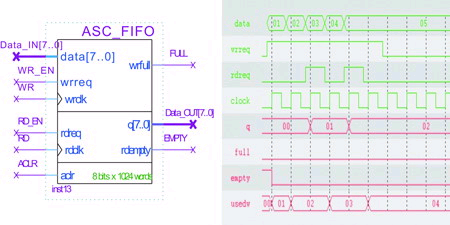

本系統(tǒng)的A/D采樣速率比較高,采樣周期達到16.7ns,而選用的華邦公司單片機77E58,在晶振40MHz的讀寫周期是100ns,而且總線的傳輸速率又比較低,因此兩者在速度上無法匹配。在這種情況下,必須要在高速采集和低速處理之間建立相應(yīng)的緩沖途徑才能保證系統(tǒng)的正常工作。為此在A/D轉(zhuǎn)換器和單片機處理器中間加入一個先入先出式緩沖器(FIFO),以緩解高速信號和低速設(shè)備之間的接口矛盾。本設(shè)計中利用EP1K50QC208中自帶的EAB(嵌入式邏輯塊),通過Quartus II中的LPM工具直接生成兩個512*8位的FIFO,作為兩路A/D轉(zhuǎn)換器的數(shù)據(jù)緩沖。Quartus II中產(chǎn)生的圖形符號和其時序波形圖形如圖6所示。FIFO的輸入信號有數(shù)據(jù)輸入信號,直接和A/D轉(zhuǎn)換器的輸入相連下;寫信號和寫使能信號,寫信號和上述頻率選擇信號相連,可以以合適的速率將數(shù)據(jù)寫入FIFO,寫使能設(shè)置為永遠(yuǎn)有效;讀信號和讀使能信號,這都有單片機發(fā)出的控制信號給出;異步清零信號則在每次寫FIFO前將其清空。輸出信號有數(shù)據(jù)信號,和單片機的數(shù)據(jù)線相連,傳送數(shù)據(jù);滿標(biāo)志信號,當(dāng)有效時停止對FIFO的寫操作;空標(biāo)志信號,當(dāng)有效時停止對FIFO的讀操作。

圖6 FIFO圖形符號和其時序波形圖

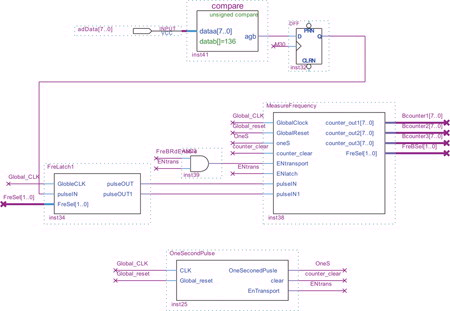

圖7 測頻模塊的符號圖

頻率測量模塊設(shè)計

圖8 雙通道波形顯示

頻率測量模塊在本系統(tǒng)中起著非常重要的作用,它不僅決定著采樣頻率,還決定液晶顯示屏幕的基本時間基準(zhǔn)。測量頻率其實就是單位時間內(nèi)的計數(shù)。在本設(shè)計中,測頻模塊的具體設(shè)計思路為:首先將A/D轉(zhuǎn)換器轉(zhuǎn)換后的數(shù)據(jù)通過一個比較器得到測頻脈沖,由于本設(shè)計中的A/D將0V電壓轉(zhuǎn)換為0x80,為避免在0V附近的小信號振蕩造成測頻誤差,將比較器的固定比較值設(shè)定為0x88。然后將測頻脈沖通過一個D觸發(fā)器同步后便開始計數(shù),在計數(shù)過程中為避免尖脈沖或毛刺信號造成對計數(shù)的影響,根據(jù)上次測頻的結(jié)果選擇合適的過濾脈寬,即比給定脈沖寬度小的信號脈沖將不會被計數(shù),提高了整個測量的精度。整個測頻模塊的符號圖如圖7所示。在圖7中,compare為比較模塊,然后經(jīng)過觸發(fā)器同步后,通過脈寬過濾模塊(FreLatch1)后到計數(shù)測頻模塊(MeasureFrequency),測量得到的數(shù)據(jù)通過八位寄存器counter_out1、counter_out2和counter_out3輸出。OneSecondPulse模塊為產(chǎn)生1s脈沖的模塊,為計數(shù)提供基準(zhǔn)參考脈沖。

液晶顯示及鍵盤模塊

在本次設(shè)計中,我們選用內(nèi)置SED1335控制器的液晶顯示模塊MS320240B,分辨率為320*240。不僅可以單獨的進行文本顯示或圖形顯示,還可以進行圖形文本合成方式顯示。在本系統(tǒng)中能夠把被測信號的波形、兩個游標(biāo)與波形相交點的電壓值及時間值顯示在液晶屏上。在液晶屏的顯示如圖8所示。

在實現(xiàn)人機通信功能的單片機通信輸入設(shè)備中,最簡單的是由按鍵組成的開關(guān)矩陣構(gòu)成的鍵盤,它隨時可以發(fā)出各種控制命令和進行數(shù)據(jù)輸入。通常按鍵所用為機械開關(guān),有很多缺點,主要是按鍵被按下或彈起時都會有輕微的抖動,抖動時間和開關(guān)的機械特性有關(guān),一般為5ms~10ms。為了避免在抖動期間掃描鍵盤得到錯誤的行值和列值,一般在檢測到有鍵按下后延時10ms再進行掃描。在本設(shè)計中,采用一個3*8的行列式鍵盤,發(fā)出各種命令來對采集器進行類似于示波器按鈕的操作。

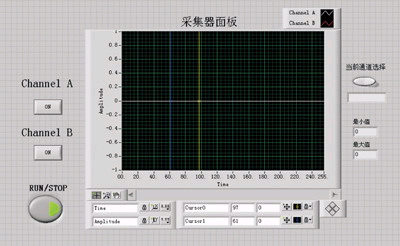

圖9 簡易示波器的上位機控制面板

USB通信單元

本次設(shè)計采用Cypress公司的CY7C68013芯片實現(xiàn)USB傳輸模塊的設(shè)計,CY7C68013是符合USB2.0標(biāo)準(zhǔn)的芯片。通過USB總線把采集的數(shù)據(jù)實時的傳遞給計算機,便于上位機也可以實時的顯示波形,還可以很方便的存儲數(shù)據(jù)。

上位機應(yīng)用程序設(shè)計

在上位機中利用計算機強大的計算能力和圖形環(huán)境,建立圖形化的軟面板來替代常規(guī)的儀器控制面板。軟面板上具有與實際儀器相似的開關(guān)、指示燈及其它控制部件。用戶通過鼠標(biāo)或鍵盤操作軟面板,檢驗儀器的性能和可操作性。同時,用戶不用編寫測試程序, 就可以可進行測試、測量,實現(xiàn)了測試的自動化、智能化。

在本設(shè)計中采用LabVIEW編寫上位機圖應(yīng)用程序。簡易示波器的上位機控制面板如圖9所示,它主要實現(xiàn)雙通道波形顯示功能。顯示面板采用游標(biāo)來進行電壓和時間的測量,可以減小人為的讀數(shù)誤差提高測量準(zhǔn)確度。當(dāng)兩個通道同時顯示時,可以通過前面板上的“當(dāng)前通道選擇”按鈕來選擇要顯示的通道的參數(shù)。RUN/STOP按鍵能夠啟動和停止數(shù)據(jù)采集顯示模塊,便于操作和讀數(shù)。前面板還帶有拖拉和縮放按鈕,方便查看圖形。

結(jié)語

本文是基于FPGA的簡易數(shù)字示波器系統(tǒng)的硬件/軟件的設(shè)計思路和設(shè)計方案。此系統(tǒng)設(shè)計完成后,測試表明系統(tǒng)可以將采集到的數(shù)據(jù)通過軟件程序控制轉(zhuǎn)換成相應(yīng)的波形顯示出來,顯示的波形和輸入信號的波形基本一致,能夠?qū)崿F(xiàn)數(shù)據(jù)采集、緩存、傳輸及波形顯示等便攜式采集系統(tǒng)的基本功能,具有非常廣闊的應(yīng)用前景。