引言

隨著人們對實時信號處理要求的不斷提高和大規模集成電路的迅速發展,作為數字信號處理核心和標志的數字信號處理器DSP芯片得到了快速的發展和應用。它不但可以廣泛應用于通信系統、圖形/圖像處理、雷達聲納、醫學信號處理等實時信號處理領域。就ADI公司而言,繼16-bit定點ADSP21xx和32-bit浮點ADSP21xxx系列之后,日前又推出了TigerSHARC系列的新型器件。本文介紹使用該系列中的ADSP-TS201S芯片實現一個圖像采集處理系統的設計方案。

系統總體方案

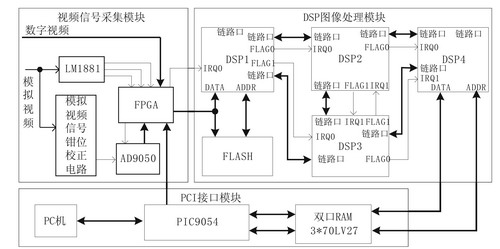

該系統可以完成圖像的采集、處理和顯示,從而實現目標識別與跟蹤的智能信號處理。該系統是對攝像機數字,模擬兩路視頻數據進行采集,處理后通過PCI總線在PC機上顯示出來。整個系統主要由視頻信號采集模塊、DSP圖像處理模塊、PCI接口模塊三個部分組成(圖1)。

圖1 圖像采集處理系統框圖

系統的各個功能模塊電路設計

·視頻信號采集模塊

攝像機提供兩路視頻信號:一路模擬視頻,一路數字視頻。

模擬視頻信號經過鉗位校正、放大后,將信號送入到A/D轉換器,再經FPGA鎖存后將視頻信號發送給DSP1;經視頻同步分離電路,由LM1881分離出模擬視頻的行、場同步信號,用于控制視頻數據采集到DSP1,以便進行圖像處理。鉗位校正、視頻同步電路如圖2所示。模擬視頻經運放輸入,將中心電平調到3.3V,加到A/D輸入端。A/D轉換后的數據進入FPGA鎖存。運放均采用ADI公司的AD8047AR,A/D轉換器采用ADI公司的AD9050。AD9050為10位A/D轉換器,取其高8位進入FPGA。采樣時鐘12MHz,與數字視頻信號相同。由FPGA對48MHz時鐘四分頻產生。

圖2 模擬視頻輸入轉換電路

攝像機的數字視頻信號為14對差分信號,經FPGA將差分信號轉換為單端信號,并鎖存數據。每個象素14位,每幀320×240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有將差分信號轉單端信號的專用I/O口。鎖存在FPGA的數字,模擬兩路視頻信號根據工作模式選擇輸出到DSP1數據總線上,由DSP1讀入處理,數據速率與模擬視頻的采樣速率,數字視頻的數據速率相同。工作模式選擇,開關控制通過PIC9054引入到FPGA。

·DSP處理器模塊

DSP處理器陣列模塊主要由4片高速高性能的DSP處理芯片ADSP-TS201S組成多DSP處理器系統,ADSP-TS201S性能如下:

基本性能指標如下:

● 600MHz運行速度時,內核指令周期1.67ns

● 24M bits片上DRAM,分為6個4M bits塊(128K words X 32 bits)

● 片內雙運算模塊,每個都包含一個ALU、一個乘法器、一個移位器和一個寄存器組

● 雙整數ALU提供數據尋址和指針操作功能

● 片內

提供14通道DMA、外部口、4個鏈路口、SDRAM控制器、可編程標志引腳、2個定時器

● 片上仲裁系統可實現8個TigerSHARC DSP的無縫連接

● 內部3條互相獨立的128位總線

● 外部數據總線64位,地址總線32位

● 每秒48億次40位寬的MAC運算或每秒12億次80位寬的MAC運算;1024點復數FFT(基2)時間15.7us

● 外部端口 1G字節每秒;鏈路口(每個)1G字節每秒

DSP處理器陣列模塊中DSP1是用來整理所收集到的視頻信號,并進行相應的預處理后,將數據分發送到后面的DSP,進行進一步的處理。

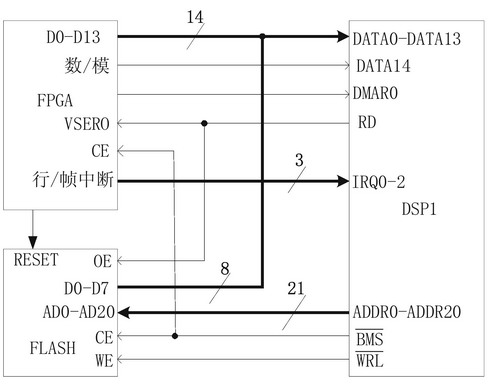

DSP1并行口應接FPGA輸出的視頻數據,還要接FLASH,完成DSP加載。DSP1的IRQ0,IRQ1分別作視頻輸入的幀中斷和行中斷,接到FPGA。其連接電路如下圖3所示。

FLASH選用AMD公司的AM29LV017D,為2M x 8-Bit的存儲器,可通過DSP1對FLASH編程,要保證在FLASH讀寫時,FPGA的數據輸出總線D0~D13為高阻,反之,在數據通道運行時,也應使FLASH輸出為高阻,故用BMS來選片FLASH。

圖3 DSP1與FPGA,FLASH 連接圖

DSP處理器陣列模塊中DSP2和DSP3是用來實現圖像處理中的主要算法。DSP2和DSP3分別用鏈路口與DSP1連接,接收由DSP1傳送來的數據,DSP2和DSP3也分別用鏈路口連接DSP4,通過鏈路口將處理的數據傳送給DSP4,進行下一步處理和數據整理。另外,DSP2和DSP3也直接采用鏈路口連接,實現DSP2和DSP3之間的通道,從而可以方便地將DSP2和DSP3配置成流水線或并行處理模式。

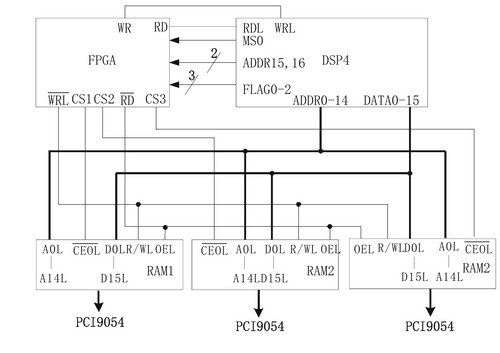

DSP處理器陣列模塊中DSP4接收DSP2和DSP3發送來的數據,進行進一步處理后,將最后處理的數據通過數據總線發送到雙端口RAM,通過PCI接口芯片PCI9054,將數據發送給PC機。該雙端口RAM采用3片IDT70LV27(32K x 16-Bit),組成96Kx 16-Bit方式,保證一次寫完一幀(320×240個象素,每個象素兩個字節),當DSP4寫滿一幀圖像數據后,向PC機產生中斷,請求PC機將數據讀走,當PC機讀取完一幀圖像數據后,應提供相應的應答,允許DSP4刷新雙口RAM。DSP陣列機互連電路如圖1所示,DSP4與雙口RAM的連接如圖4所示。DSP4接3片雙口RAM,與PCI9054形成接口。DSP4的FLAG0作為通過PCI9054輸出的視頻傳輸握手信號。

ADSP-TS201S陣列機采用鏈路口互連方式,在主要的數據傳輸方向設置了數據傳輸啟動FLAG信號到接收方的IRQ產生中斷,以便更好的實現時序的匹配。

DSP1引入了工作/關閉選擇(FLAG1輸入),數據模式(數字/模擬)選擇由DATA14引腳讀入,可以在一幀數據開始輸入時,讀入一次數據選擇模式,此后就可以不再處理了。

圖4 DSP4與雙口RAM接口

·PCI接口模塊

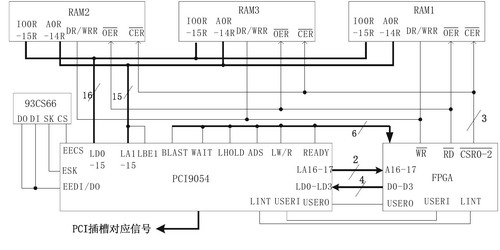

PCI接口采用PLX公司的PCI9054接口芯片,32位,33MHZ數據總線。RAM1,2,3三片雙口RAM(IDT70LV27)作DSP4數據輸出緩存。由PCI9054讀入到PC機。在雙口RAM內,相當于右半邊接口,PCI9054其電路連接如圖5所示。PCI9054對應著PCI槽的信號,按PCI槽名稱對應連接,加載EEPROM選用93CS66。 將LD0~LD3引入到FPGA內,可以單次I/O寫方式,輸出4位狀態,作主機控制。開、關機,數字視頻/模擬視頻選擇以A16~17的譯碼之一作地址選擇。FPGA讀入后,譯碼成控制信號輸出。

圖5 PCI9054與雙口RAM,FPGA連接

結語

基于ADSP-TS201S的圖像采集處理系統能夠完成圖像的高速處理,實現圖像的實時顯示,目標跟蹤。在實際應用中該系統工作穩定,達到預想效果。