通常,我們更喜歡把臺(tái)式機(jī)/筆記本電腦的復(fù)雜指令集叫做CISC,把智能手機(jī)的精簡(jiǎn)指令集叫做RISC。戴爾和蘋果等 OEM 一直在其筆記本電腦中使用 x86 CISC 處理器。讓我在這里解釋筆記本電腦的設(shè)計(jì)方法。主板以多核CISC處理器為主要部件,連接GPU、RAM、存儲(chǔ)內(nèi)存等子系統(tǒng)和I/O接口。操作系統(tǒng)在多核處理器上并行運(yùn)行多個(gè)應(yīng)用程序,管理內(nèi)存分配和 I/O 操作。

這就是我們使用處理器實(shí)現(xiàn)任何電子系統(tǒng)的方式。然而,我們更喜歡使用 RISC 處理器的智能手機(jī)系統(tǒng)級(jí)芯片,因?yàn)樗兄谖覀儨p小主板的尺寸和功耗。幾乎整個(gè)具有多核 RISC CPU、GPU、DSP、無(wú)線和接口子系統(tǒng)、SRAM、閃存和 IP 的系統(tǒng)都在 SoC 上實(shí)現(xiàn)。OEM Apple 正在遵循這款智能手機(jī)的 SoC 設(shè)計(jì)方法,甚至將他們的 MAC 筆記本作為 OEM 潮流引領(lǐng)者。所有最新的 MAC 書籍都使用他們的 M 系列 SoC,這些 SoC 使用 ARM 的 RISC 處理器。

因此,很明顯,英特爾的 x86 或 ARM 的 RISC 處理器的專有 ISA 一直是 Apple、戴爾、三星等 OEM 的選擇,但現(xiàn)在為什么我們需要像 RISC-V 這樣的開放 ISA,而不是所有這些經(jīng)過(guò)充分驗(yàn)證的ISA。

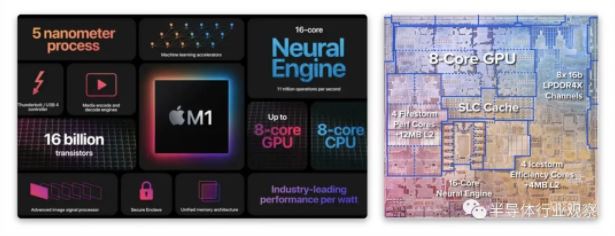

在今天的情況下,每個(gè)人都將 SoC 用于他們的筆記本電腦和智能手機(jī)。這種復(fù)雜的 SoC 需要通用處理器和專用處理器。為了實(shí)現(xiàn)像 Apple 的 M 系列 SoC 這樣的芯片,我們需要不同種類的處理器,如 RISC CPU、GPU、DSP、安全處理器、圖像處理器、機(jī)器學(xué)習(xí)加速器、安全和神經(jīng)引擎,基于來(lái)自多個(gè) IP 的各種通用和專用 ISA供應(yīng)商,如圖1所示。

圖 1:Apple M1 SoC 參考:AnandTech

在這種情況下,主要挑戰(zhàn)是: 1.選擇并與多家 IP 供應(yīng)商合作 2.不同的 IP 供應(yīng)商可能有不同的 IP 許可方案,工程師將無(wú)法自由地定制 ISA 和設(shè)計(jì),因?yàn)樗麄兏敢鉂M足他們的設(shè)計(jì)目標(biāo)。 3.所有專門的 ISA 都不會(huì)持續(xù)/生存很長(zhǎng)時(shí)間,從而影響長(zhǎng)期產(chǎn)品支持計(jì)劃和路線圖。 4.此外,涉及多個(gè) ISA 和工具鏈的軟件/應(yīng)用程序開發(fā)和更新將具有挑戰(zhàn)性。 RISC-V 是一種具有多種擴(kuò)展功能的通用免許可開放式 ISA。它是一個(gè) ISA,分為一個(gè)小的基本整數(shù) ISA,可用作定制加速器和可選標(biāo)準(zhǔn)擴(kuò)展的基礎(chǔ),以支持通用軟件開發(fā)。 您可以添加自己的擴(kuò)展來(lái)實(shí)現(xiàn)您的專用處理器,或者根據(jù)需要自定義基本 ISA,因?yàn)樗情_放的。沒(méi)有許可證限制。因此,在未來(lái),我們可以僅使用一個(gè) RISC-V ISA 創(chuàng)建所有通用和專用處理器,并實(shí)現(xiàn)任何復(fù)雜的 SoC。

什么是 RISC-V,它與其他 ISA 有何不同?

RISC-V 是加州大學(xué)伯克利分校的第五個(gè)主要 ISA 設(shè)計(jì)。它是由非營(yíng)利組織 RISC-V InternaTIonal維護(hù)的開放式 ISA,涉及所有利益相關(guān)者社區(qū)以實(shí)施和維護(hù) ISA 規(guī)范、黃金參考模型和合規(guī)性測(cè)試套件。 RISC-V 不是 CPU 實(shí)現(xiàn)。它是通用處理器和專用處理器的開放式 ISA。一個(gè)完全開放的 ISA,可供學(xué)術(shù)界和工業(yè)界免費(fèi)使用。 RISC-V ISA 被分成一個(gè)小的基本整數(shù) ISA,可單獨(dú)用作定制加速器或教育目的的基礎(chǔ),以及支持通用軟件開發(fā)的可選標(biāo)準(zhǔn)擴(kuò)展 RISC-V 支持應(yīng)用程序、操作系統(tǒng)內(nèi)核和硬件實(shí)現(xiàn)的 32 位和 64 位地址空間變體。因此,它適用于所有計(jì)算系統(tǒng),從嵌入式微控制器到云服務(wù)器,如下所述。 簡(jiǎn)單的嵌入式微控制器、保護(hù)運(yùn)行 RTOS 的嵌入式系統(tǒng)、運(yùn)行操作系統(tǒng)的臺(tái)式機(jī)/筆記本電腦/智能手機(jī)以及運(yùn)行多個(gè)操作系統(tǒng)的云服務(wù)器。

二、RISC-V 基礎(chǔ) ISA

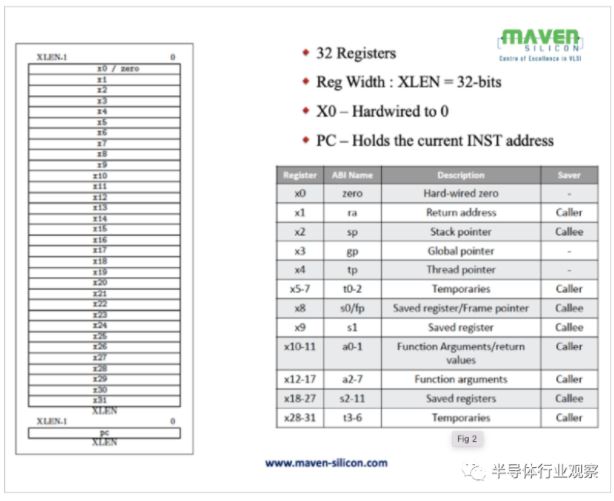

RISC-V 是一個(gè)相關(guān) ISA 家族:RV32I、RV32E、RV64I、RV128I。 RV32I/ RV32E/ RV64I/RV128I 是什么意思: RV——RISC-V 32/64/128 – 定義寄存器寬度 [XLEN] 和地址空間 I – 整數(shù)基 ISA 32 個(gè)用于所有基本 ISA 的寄存器 E – 嵌入式:只有 16 個(gè)寄存器的基本 ISA (1)RISC-V 寄存器: 所有基本 ISA 都有 32 個(gè)寄存器,如圖 2 所示,除了 RV32E。只有RV32E base ISA對(duì)于簡(jiǎn)單的嵌入式微控制器只有16個(gè)寄存器,但寄存器寬度仍然是32位。 寄存器 X0 硬接線為零。稱為程序計(jì)數(shù)器的特殊寄存器保存要從內(nèi)存中獲取的當(dāng)前指令的地址。 如圖 2 所示,RISC-V 應(yīng)用程序二進(jìn)制接口,ABI 定義了寄存器的標(biāo)準(zhǔn)功能。為了簡(jiǎn)單和一致,軟件開發(fā)工具通常使用 ABI 名稱。根據(jù) ABI,額外的寄存器專用于 X0 到 X15 范圍內(nèi)的保存寄存器、函數(shù)參數(shù)和臨時(shí)變量,主要用于 RV32E 基礎(chǔ) ISA,它只需要前 16 個(gè)寄存器來(lái)實(shí)現(xiàn)簡(jiǎn)單的嵌入式微控制器。但是 RV32I 基礎(chǔ) ISA 將擁有所有 32 個(gè)寄存器 X0 到 X31。

圖 2:RISC-V 寄存器和 ABI 名稱參考:RISC-V 規(guī)范

(2)RISC-V內(nèi)存: RISC-V hart [硬件線程/核心] 具有用于所有內(nèi)存訪問(wèn)的 2^XLEN 字節(jié)的單字節(jié)可尋址地址空間。XLEN 表示整數(shù)寄存器的位寬度:32/64/128。 內(nèi)存字定義為 32 位(4 字節(jié))。相應(yīng)地,半字為16位(2字節(jié)),雙字為64位(8字節(jié)),四字為128位(16字節(jié))。 內(nèi)存地址空間是循環(huán)的,因此地址 2^XLEN -1 處的字節(jié)與地址零處的字節(jié)相鄰。因此,由硬件完成的內(nèi)存地址計(jì)算忽略溢出,而是環(huán)繞模 2^XLEN。 RISC-V 基礎(chǔ) ISA 具有小端或大端存儲(chǔ)系統(tǒng),特權(quán)架構(gòu)進(jìn)一步定義了大端操作。指令作為 16 位小尾數(shù)法包的序列存儲(chǔ)在內(nèi)存中,而不管內(nèi)存系統(tǒng)的字節(jié)順序如何。

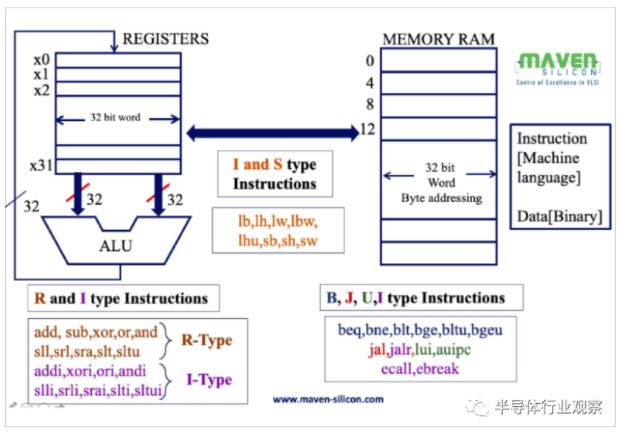

(3)RISC-V 加載存儲(chǔ)架構(gòu)

您可以可視化基于 RISC-V 寄存器和內(nèi)存的 RISC-V 加載存儲(chǔ)架構(gòu),如下圖 3 所示。 RISC-V處理器根據(jù)PC中的地址從主存中取/載指令,譯碼32位指令,然后ALU進(jìn)行算術(shù)/邏輯/內(nèi)存讀寫操作。ALU 的結(jié)果將存儲(chǔ)回其寄存器或內(nèi)存中。

圖 3:RISC-V 加載存儲(chǔ)架構(gòu)

(4)RISC-V RV32 I 基礎(chǔ) ISA

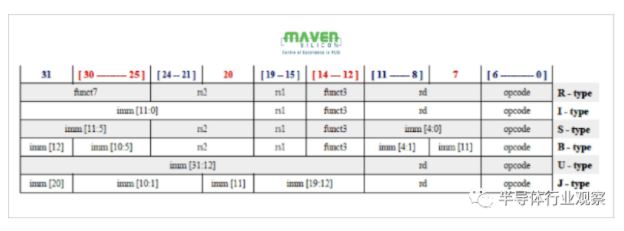

RV32I base ISA 只有 40 條 Unique InstrucTIons,但簡(jiǎn)單的硬件實(shí)現(xiàn)只需要 38 條指令。RV32I指令可分為: R-Type:注冊(cè)到注冊(cè)說(shuō)明 I-Type:立即注冊(cè)、加載、JLR、Ecall 和 Ebreak S型:商店 B型:分支 J型:跳躍和鏈接 U 型:立即加載/添加上層

圖 4:RV32I 基本 ISA 指令格式

(5)用于優(yōu)化 RTL 設(shè)計(jì)的 RISC-V ISA

在這里,我想解釋一下 RISC-V ISA 如何使我們能夠?qū)崿F(xiàn)優(yōu)化的寄存器傳輸級(jí)設(shè)計(jì),以滿足低功耗和高性能的目標(biāo)。 如圖 4 所示,RISC-V ISA 在所有格式中將源(rs1 和 rs2)和目標(biāo)(rd)寄存器保持在相同位置以簡(jiǎn)化解碼。 立即數(shù)總是經(jīng)過(guò)符號(hào)擴(kuò)展,并且通常被打包到指令中最左邊的可用位,并且已被分配以降低硬件復(fù)雜性。尤其是, 所有立即數(shù)的符號(hào)位總是在指令的第 31 位以加速符號(hào)擴(kuò)展電路。 符號(hào)擴(kuò)展是對(duì)立即數(shù)最關(guān)鍵的操作之一(特別是對(duì)于 XLEN>32),在 RISC-V 中,所有立即數(shù)的符號(hào)位始終保存在指令的第 31 位中,以允許符號(hào)擴(kuò)展與指令解碼并行進(jìn)行。 為了加快解碼速度,基礎(chǔ) RISC-V ISA 將最重要的字段放在每條指令的同一位置。正如您在指令格式表中所見(jiàn),

主要操作碼總是在位 0-6 中。

目標(biāo)寄存器(如果存在)始終位于位 7-11 中。

第一個(gè)源寄存器(如果存在)始終位于第 15-19 位。

第二個(gè)源寄存器(如果存在)始終位于第 20-24 位。

但是為什么立即位會(huì)被打亂呢?想想解碼直接場(chǎng)的物理電路。由于它是硬件實(shí)現(xiàn),因此這些位將被并行解碼;輸出立即數(shù)中的每一位都有一個(gè)多路復(fù)用器來(lái)選擇它來(lái)自哪個(gè)輸入位。多路復(fù)用器越大,成本越高,速度也越慢。 值得注意的是,只需要主要操作碼(位 0-6)就可以知道如何解碼立即數(shù),因此立即數(shù)解碼可以與指令其余部分的解碼并行完成。 (6)RV32I 基本 ISA 指令

RISC-V ISA 擴(kuò)展

此處列出了所有 RISC-V ISA 擴(kuò)展:

圖 5:RISC-V ISA 擴(kuò)展

我們遵循 RISC-V 處理器的命名約定,如下所述:

RISC-V 處理器:RV32I、RV32IMAC、RV64GC

RV32I:整數(shù)基礎(chǔ) ISA 實(shí)現(xiàn) RV32IMAC:整數(shù)基礎(chǔ) ISA + 擴(kuò)展:[乘法 + 原子 + 壓縮]

RV64GC:64 位 IMAFDC [G-通用:IMAFD]

整數(shù) 64 位基本 ISA + 擴(kuò)展:[乘法 + 原子 + SP 浮動(dòng) + DP 浮動(dòng) + 壓縮]

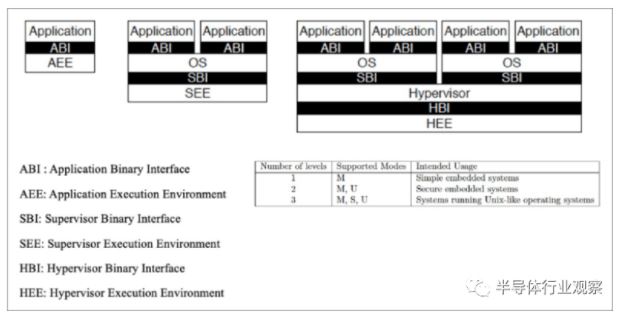

RISC-V 特權(quán)架構(gòu)

RISC-V 特權(quán)架構(gòu)涵蓋了 RISCV 系統(tǒng)的所有方面,超出了我到目前為止所解釋的非特權(quán) ISA。特權(quán)架構(gòu)包括特權(quán)指令以及運(yùn)行操作系統(tǒng)和連接外部設(shè)備所需的附加功能。 根據(jù) RISC-V 特權(quán)規(guī)范,我們可以實(shí)現(xiàn)從簡(jiǎn)單的嵌入式控制器到復(fù)雜的云服務(wù)器的不同類型的系統(tǒng),如下所述。 應(yīng)用程序執(zhí)行環(huán)境 – AEE:“裸機(jī)”硬件平臺(tái),其中 harts 直接由物理處理器線程實(shí)現(xiàn),指令可以完全訪問(wèn)物理地址空間。硬件平臺(tái)定義了一個(gè)從上電復(fù)位開始的執(zhí)行環(huán)境。示例:簡(jiǎn)單且安全的嵌入式微控制器 主管執(zhí)行環(huán)境——參見(jiàn):RISC-V 操作系統(tǒng),通過(guò)將用戶級(jí) harts 多路復(fù)用到可用的物理處理器線程并通過(guò)虛擬內(nèi)存控制對(duì)內(nèi)存的訪問(wèn)來(lái)提供多個(gè)用戶級(jí)執(zhí)行環(huán)境。

示例:運(yùn)行類 Unix 操作系統(tǒng)的桌面等系統(tǒng)

Hypervisor ExecuTIon Environment – HEE:RISC-V hypervisor,為來(lái)賓操作系統(tǒng)提供多個(gè)管理級(jí)執(zhí)行環(huán)境。

示例:運(yùn)行多個(gè)guest操作系統(tǒng)的云服務(wù)器

圖 6:RISC-V 特權(quán)軟件堆棧

參考:RISC-V 規(guī)范 此外,RISC-V 特權(quán)規(guī)范定義了各種控制和狀態(tài)寄存器 [CSR],以實(shí)現(xiàn)各種功能,如任何系統(tǒng)的中斷、調(diào)試和內(nèi)存管理設(shè)施。您可能需要參考規(guī)范以探索更多信息。

如本文所述,我們可以使用通用的開放式 RISC-V ISA 高效地實(shí)現(xiàn)任何系統(tǒng),從簡(jiǎn)單的物聯(lián)網(wǎng)設(shè)備到復(fù)雜的智能手機(jī)和云服務(wù)器。由于單片半導(dǎo)體縮放失敗,專業(yè)化是提高計(jì)算性能的唯一途徑。開放式 RISC-V ISA 是模塊化的,支持自定義指令,使其成為創(chuàng)建各種專用處理器和加速器的理想選擇。

隨著 IEEE 標(biāo)準(zhǔn)通用驗(yàn)證方法論的出現(xiàn),我們?cè)谛酒?yàn)證方面取得了巨大成功,開放的 RISC-V ISA 也將繼承各種專有 ISA 的所有優(yōu)點(diǎn),成為行業(yè)標(biāo)準(zhǔn) ISA,引領(lǐng)我們走向未來(lái)開放的計(jì)算時(shí)代。您準(zhǔn)備好使用 RISC-V 專業(yè)知識(shí)迎接這個(gè)美好的未來(lái)了嗎?

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<