摘 要: 介紹用FPGA實現數字通信中的交、解交織器的一種比較通用的方案,詳細說明了設計中的一些問題及解決辦法。還介紹了一種實現FPGA中信號延時的方法。

關鍵詞: 交織器與解交織器 FPGA技術 地址序列 最小時延 信號延時

在現代數字通信系統中,FPGA的應用相當廣泛。尤其是在對基帶信號的處理和整個系統的控制中,FPGA不但能大大縮減電路的體積,提高電路的穩定性,而且先進的開發工具使整個系統的設計調試周期大大縮短。

1 交織器與解交織器的原理

數字通信中經常用信道編碼來提高數據傳輸的可靠性,其中一些信道編碼加入了交織模塊,以進一步提高抗干擾性能。交織器的主要作用就是將原始數據序列打亂,使得交織前后數據序列的相關性減弱,這樣做很突出的一個優點便是大大降低了數據突發錯誤的影響。在現代的高效編碼調制技術中,無論是級聯編碼還是Turbo編碼中都要使用交織器。

數字通信中常用的交織器按交織方式可分為分組交織器和隨機交織器兩種,按交織對象分可分為字節交織和位交織。本文所介紹的實現方案主要針對字節交織器。下面用一個模型來說明交織器的工作過程。設外碼RS碼字長度為n=7,交織器深度Id=4,相鄰碼字之間的交錯字節數di=[![]() ]=Smallest Integer≥

]=Smallest Integer≥![]() =2,則交織器的功能如下圖1所示。

=2,則交織器的功能如下圖1所示。

輸入碼字按行排列,按列輸出,圖中“*”為無效數據,即交織器輸出的前端有一些無效數據。

解交織器將交織器打亂的字節序列重新排列恢復原始碼字。如圖1,即將串行輸入的字節序列先按列方式讀入,再逐行將碼字讀出。從圖中可以看出,行與行的碼字間均有di字節交錯,這種斜交織方式的優點可以減小系統時延。

2 交織器的實現

2.1 實現模型:

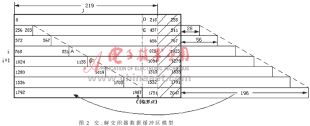

在本課題中,交織器的幾個參數分別為:n=219,Id=8,di=[![]() ]=28。圖2是實現交織器模型。

]=28。圖2是實現交織器模型。

圖中粗線內的方塊區域為實現交織器所必須的一塊數據緩沖區(存儲器),考慮到交織器的功能特性是須對此緩沖區同時讀寫,故選用雙口RAM實現最好,因為1024<219×8<2048,故容量用2Kbytes即可。模型中所標識的數字是存儲器的地址,畫斜線的區域為空閑緩存區,右邊存儲器外虛線下數據實際上是存儲在存儲器左下角的區域內。交織器實際工作時,一邊按寫地址序列向緩存區中寫入數據,另一邊按讀地址序列讀出。圖2模型的寫地址序列為:0,1,2...218,284,285...437,256,257...283,568,569...656,512,513...567,852......,依次寫入每行,直到1987,下一字節再從0地址開始,循環寫入。讀地址序列為:0,256,512,768,1024...1792,1,257,513......,直到1751地址,再從0地址開始循環。

對于解交織器,讀地址序列正好是交織器的寫地址序列,寫地址序列是交織器的讀地址序列。

2.2 FPGA的選用及實現的原理框圖

目前主要的FPGA廠商有Xilinx、Altera、AMD、Lattice、Actel、Lucent及Atmel等。Altera公司生產的FLEX 10K系列的FPGA,具有規模覆蓋范圍廣、布線資源豐富、時間可預測性好的優點,故而在數字通信系統設計中得到了廣泛的應用。此外,FLEX 10K系列芯片都具有EAB(Embeded Array Block),可以實現片內存儲器功能,若用EAB做交織器、解交織器的數據緩存區,就可以用單片FPGA完成交、解交織器的功能,從而大大減小電路的復雜度和體積。但實際應用中,由于FLEX 10K芯片的片內EAB資源有限,所以要完全實現交、解交織器,至少要選擇FLEX 10K130(內部有13萬門左右的資源)以上規模的FPGA。可是實現交織器的時序控制邏輯并不復雜,大概需要一萬門左右的資源就夠了,再加上系統其它功能塊也不過幾萬門,若使用10K130芯片就會造成資源浪費,而且成本過高。綜合考慮,決定用外部雙口RAM(IDT 7132)當作數據緩沖區,FPGA選用FLEX 10K20芯片。

圖3即為用FPGA實現交織器的原理框圖,FPGA的內部可由讀、寫地址序列發生器和時序控制器三部分組成。時序控制器主要產生雙口RAM讀寫控制信號,并決定讀、寫地址序列發生器何時啟動工作。因為解交織器僅是數據進出雙口RAM的順序不同,故上原理圖中只須變換讀、寫地址序列發生器便可構成解交織器。

3 實現中的若干問題

3.1 讀寫地址的產生問題

最一般的方案為查找表的方法。令輸入數據順序存入雙口RAM,即寫地址序列變為:0,1,2,3...1750,1751,0......,對照模型找出對應的讀地址序列。這樣重新編址的好處是使寫地址序列易于產生,可以由FPGA直接生成。將讀地址序列做成表順序存入E2PROM(或其它只讀存儲器,如Flash),需要讀雙口RAM時,FPGA產生0,1,2...1751順序序列作地址送給E2PROM,映射出的數據送給雙口RAM作讀地址。這種查找表的方法具有很好的通用性,可以適用于各類字節交織器,但缺點是須額外附加存儲器,而且E2PROM的讀取速度一般較慢,在數據傳輸速率較高的情況下不適用。

本課題中的交織器在圖2所示的模型和編址方法下,讀、寫地址序列具有較強的規律性,可以用在FPGA中構造計數器的方式來直接產生。下面介紹一下地址序列的產生方法。將11位地址分成兩部分:高3位和底8位,在物理實現上構造3位和8位計數器各一個,然后級聯起來。對于交織器的讀地址序列,具體實現時,用數據輸入時鐘DataInClk驅動3位計數器計數,3位計數器記滿同步清0時產生脈沖驅動8位計數器計數,8位計數器計到218后同步清0。交織器的寫地址序列產生稍復雜,但同樣可用兩計數器的級聯產生。

3.2 交織、解交織器的最小時延問題

無論是交織器還是解交織器,數據緩沖區的讀相對于寫必須有一個延時,這個延時即為交織器和解交織器的時延。為了盡量減小系統的時延,應使交織器和解交織器的時延降至最小。

首先分析交織器,設數據周期為T,則每個緩沖區單元的讀或寫地址的保持時間也為T。考察圖2模型中從第i行的交錯后的第一個元素A到第i+1行的元素B所用的時間,若按寫操作進行需219×T,按讀操作進行需(28×8+1)T=225T>219T。這表明若讀、寫同時從0地址開始,則緩沖區那的每個存儲單元的寫操作都在讀操作之前,從而保證每個讀出的數據都有效。這里對于交錯所產生的左下角區域元素,交織器開始工作時讀出的都是無效數據,但在循環往復的連續數據讀寫中,讀出的則是上一頁所寫碼字的部分字節,是有效數據。故在交織器中,讀、寫緩沖區可以同時開始,考慮到雙口RAM對同一單元不能同時讀寫,所以設計時令讀滯后于寫一個數據周期T,這樣交織器的最小時延為T。

解交織器的分析方法類似。由模型二可推算出,當系統寫雙口RAM的E單元時,讀從0地址單元開始,故解交織器的最小時延為:(28×7×8+1)T= 1569T。

3.3 FPGA中延時功能的實現

在FPGA的開發設計中,經常需要用到延時模塊。如本設計中,實現雙口RAM的讀寫時序時就需要。以IDT 7132的讀時序為例,時序圖如圖4所示。

無論用 還是

還是 來控制讀取,都需要

來控制讀取,都需要 或

或 保持一段低電平。令

保持一段低電平。令 保持低電平,

保持低電平, 平時為高電平,讀雙口RAM時觸發CE變為低電平,延遲一小段時間再恢復高電平。本設計產生這段延時的方法是用高頻計數器產生,具體方法為:在FPGA中設計一個計數器,取系統可用的高頻時鐘(周期小于所需延時)驅動它計數,計到設定好的終值時產生觸發脈沖。不同的計數終值可以產生不同的延時。此方法所產生的延時為高頻時鐘周期的整數倍,若高頻時鐘周期與所需延時相比很小,則延時較精確,否則只能做一粗略的延時。

平時為高電平,讀雙口RAM時觸發CE變為低電平,延遲一小段時間再恢復高電平。本設計產生這段延時的方法是用高頻計數器產生,具體方法為:在FPGA中設計一個計數器,取系統可用的高頻時鐘(周期小于所需延時)驅動它計數,計到設定好的終值時產生觸發脈沖。不同的計數終值可以產生不同的延時。此方法所產生的延時為高頻時鐘周期的整數倍,若高頻時鐘周期與所需延時相比很小,則延時較精確,否則只能做一粗略的延時。

當需要對某一信號作一段延時時,初學者往往在此信號后串接一些非門或其它門電路,此方法在分離電路中是可行的。但在FPGA中,開發軟件在綜合設計時會將這些門當作冗余邏輯去掉,達不到延時的效果。用Altera公司的Maxplus II開發FPGA時,可以通過插入一些LCELL原語來產生一定的延時,但這樣形成的延時在FPGA芯片中并不穩定,會隨溫度等外部環境的改變而改變,因此Altera并不提倡這樣做。在此,沿用上一段中的思想,可以用高頻時鐘來驅動一移位寄存器,待延時信號作數據輸入,按所需延時正確設置移位寄存器的級數,移位寄存器的輸出即為延時后的信號。此方法產生的延時信號與原信號比有誤差,誤差大小由高頻時鐘的周期來決定。對于數據信號的延時,在輸出端用數據時鐘對延時后信號重新采樣,就可以消除誤差。

總之,本文著重介紹了用FPGA實現數字通信中的交、解交織器的一種比較通用的方案。其它種類的交織器,只需更換讀、寫地址產生模塊,確定讀、寫時差即可完成。除了隨機交織器須用查找表的方式產生讀地址序列外,大部分的交織器讀、寫地址都可用本文介紹的類似方法實現,這樣既節省芯片,縮小電路體積,速度又快,調試也大大簡化。文中還介紹了一種實現FPGA中信號粗略延時的方法以供大家參考。

參考文獻

1 Intelsat Earth Station Standards (IESS) Documents IESS-310 (Rev.B),May 1997

2 王小軍編著.VHDL簡明教程.北京:清華大學出版社,1997

3 Leonardo HDL Synthesis Guide,Exemplar Logic

4 馬群生,李健航編譯.MAX Plus II 入門.清華大學Altera培訓中心,1996.4